- Y4 – аналоговый сигнал управления объектом

- Y5 – сигнал установки внешних устройств в исходное состояние

- «звуковой сигнал» – выход на источник звуковых сигналов аварии

- «индикация пульта оператора» – передача на пульт оператора значений по запросу оператора

Для преобразования аналоговых сигналов в цифровую форму используется один АЦП. Его вход может программно коммутироваться на один из входов V1-V3, для чего в схеме МПС использованы аналоговые коммутаторы.

Микросхема ППА используется для ввода данных и вывода сигналов управления коммутаторами, а также генерации сигналов Y5 и звуковой сигнализации аварии.

Микросхема ПСА используется для связи с внешней ЭВМ.

Для выдачи цифрового сигнала на ЦАП и формирования сигналов индикации на пульте оператора используются простейшие регистры-защелки, так как применение еще одного ППА нецелесообразно ввиду неполного использования его возможностей и сложности программирования.

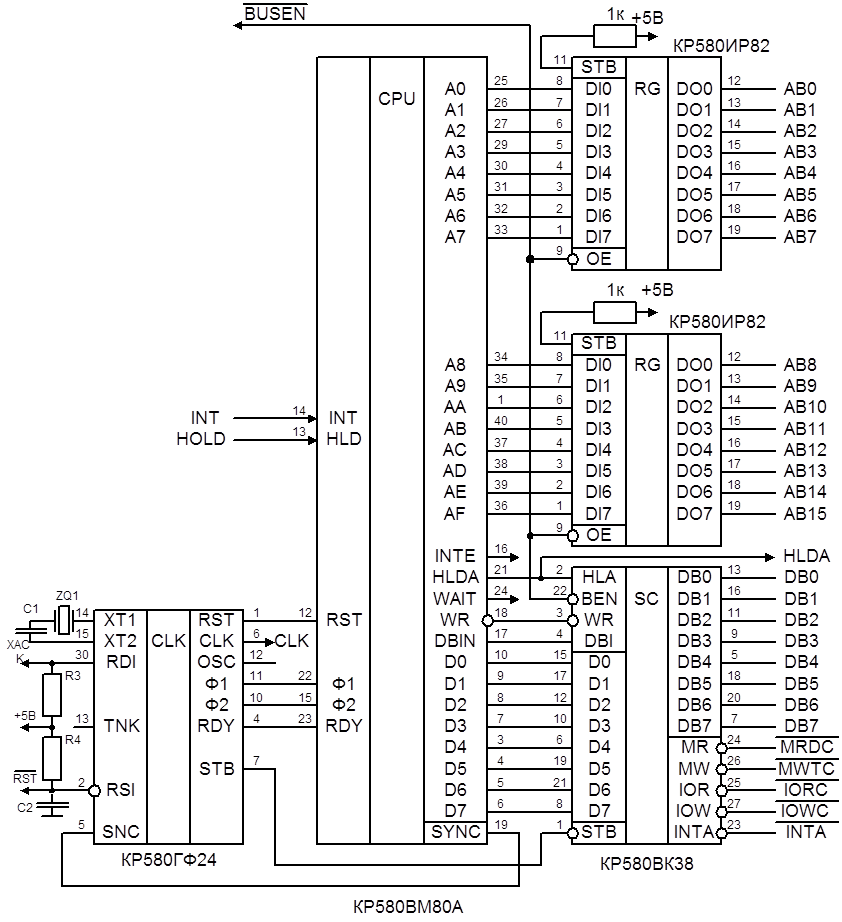

Используем распространенную типовую схему включения микропроцессора КР580ВМ80А [1,2] с генератором тактовых импульсов КР580ГФ24 и системным контроллером КР580ВК38 (рисунок 4). Данная схема обеспечивает работу процессора с формированием шин адреса, данных и управления. В качестве формирователей шины адреса используем специализированные адресные регистры КР580ИР82.

Микросхема КР580ГФ24 построена так, что частота следования синхроимпульсов Ф1 и Ф2 будет в девять раз меньше частоты кварцевого резонатора. Таким образом, чтобы получить оптимальную для микропроцессора частоту 2 МГц, нужно использовать кварцевый резонатор частотой 18 МГц.

Из-за индуктивного характера сопротивления кварцевого резонатора частота генерации несколько снижается. Для компенсации этого эффекта последовательно с резонатором включается конденсатор емкостью 15-30 пФ.

С вывода 6 генератора тактовых импульсов снимается сигнал тактирования других устройств системы. Сигнал по уровню совместим с ТТЛ и имеет ток нагрузки до 15 мА.

Сигнал RST с вывода 1 микросхемы используется для начального сброса устройств системы. Длительность его определяется параметрами R4 и С2 и должна быть не менее 0,3 с. Сигнал вырабатывается при включении питания или подаче на вход RSI нулевого потенциала.

|

Рисунок 4. Принципиальная схема системного модуля

В данной микропроцессорной системе применяется постоянная память программ (ПЗУ) и оперативная память данных. Доступ к памяти организован по Фон-Неймановской архитектуре – адресное пространство программ и данных неразличимо.

Для данного применения микропроцессора достаточно постоянной памяти программ объемом 512 байт (см. программу). В качестве микросхемы памяти выберем микросхему ПЗУ К556РТ5 (емкость 512X8 бит) [6]. Данная микросхема является однократно программируемым ПЗУ, и по уровням сигналов совместима с логикой ТТЛ. Микросхема имеет прямые и инверсные входы выборки кристалла (E).

Так как алгоритм работы микропроцессорной системы не требует хранения больших объемов оперативных данных, то в целях экономии следует применять ОЗУ небольшой емкости. Так, емкости в 16 байт вполне хватает для хранения некоторых промежуточных данных и организации стека достаточной глубины вложенности. В качестве кристаллов ОЗУ можно использовать две статические ТТЛ - микросхемы К531РУ11 (по 16X4 бит) [6]. Для выборки микросхемы имеют инверсные входы записи (WE) и чтения (OE). В БИС использованы раздельные входы и выходы данных, которые для подключения к шине данных необходимо объединить между собой, что допустимо, так как в режиме чтения выходы находятся в Z-состоянии.

Для обеспечения начального запуска процессора память программ необходимо расположить в начальных адресах памяти, т.е. по адресам 0000h-01FFh. ОЗУ можно располагать в любом месте. Для удобства запоминания и построения схемы дешифратора расположим ОЗУ с адреса 1000h, в таком случае выборка ОЗУ будет осуществляться одной активной адресной линией A12. Карта памяти микропроцессорной системы в таком случае приведена в таблице 1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.