|

Таблица 1 Карта памяти МПС |

|||||||||||||||||

|

Память |

Линии шины адреса |

Адрес |

|||||||||||||||

|

15 |

14 |

13 |

12 |

11 |

10 |

9 |

8 |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

||

|

ПЗУ |

x |

x |

x |

0 |

x |

x |

x |

A |

A |

A |

A |

A |

A |

A |

A |

A |

0000-01FF |

|

ОЗУ |

x |

x |

x |

1 |

x |

x |

x |

x |

x |

x |

x |

x |

A |

A |

A |

A |

0100-010F |

x – произвольное состояние линии (условно 0), А – значащий бит адреса

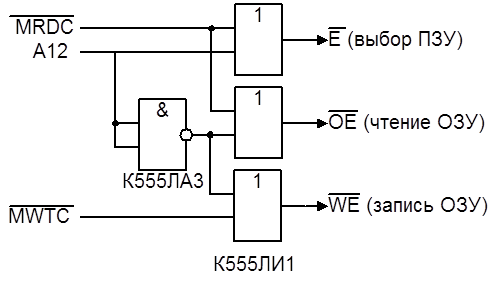

При построении схемы дешифрации памяти необходимо учесть, что выборка памяти должна происходить при активном уровне на одной из линий MRDC или MWTC. Дешифрация должна происходить в соответствии с таблицей (таблица 2)

|

Таблица 2 Формирование сигналов при обращении к памяти |

||||||

|

Операция |

____ MRDC |

____ MWTC |

A12 |

_ E |

__ WE |

__ OE |

|

Чтение ПЗУ |

0 |

1 |

0 |

0 |

1 |

1 |

|

Чтение ОЗУ |

0 |

1 |

1 |

1 |

1 |

0 |

|

Запись ОЗУ |

1 |

0 |

1 |

1 |

0 |

1 |

|

Попытка записи ПЗУ |

1 |

0 |

0 |

1 |

1 |

1 |

|

Работа с портами |

1 |

1 |

x |

1 |

1 |

1 |

Схема дешифрации памяти, разработанная в соответствии с вышеприведенными замечаниями, приведена на рисунке 5.

|

В подсистеме ввода вывода будут работать следующие функциональные модули:

- программируемый контроллер прерываний (КР580ВН59)

- программируемый интервальный таймер (КР580ВИ53)

- программируемый параллельный интерфейс (КР580ВВ55А)

- программируемый последовательный интерфейс (КР580ВВ51А)

- регистр ЦАП

- регистр индикации

Дешифрацию портов будем производить по линиям шины адреса A12, А11 и А10. С учетом этого составим таблицу адресации портов разрабатываемой МПС (таблица 3). При этом необходимо учитывать, что обращение к микросхеме должно происходить при надлежащей комбинации сигналов на адресных линиях и активных сигналах IORC или IOWC, а также то, что при адресации портов командами IN и OUT 8-битный адрес порта дублируется в старшей половине адресной шины.

|

Таблица 3 Адресация портов ввода-вывода МПС |

|||||||||

|

Выбираемая микросхема |

Состояние линий |

Базовый адрес |

|||||||

|

A15 (А7) |

A14 (А6) |

А13 (А5) |

А12 (А4) |

A11 (А3) |

A10 (А2) |

A9 (А1) |

A8 (А0) |

||

|

ПИТ |

x |

x |

x |

0 |

0 |

0 |

x |

x |

E0 |

|

ПКП |

x |

x |

x |

0 |

0 |

1 |

x |

x |

E4 |

|

Регистр ЦАП |

x |

x |

x |

0 |

1 |

0 |

x |

x |

E8 |

|

Рег. инд. |

x |

x |

x |

0 |

1 |

1 |

x |

x |

EC |

|

ППА |

x |

x |

x |

1 |

0 |

0 |

x |

x |

F0 |

|

запуск АЦП |

x |

x |

x |

1 |

0 |

1 |

x |

x |

F4 |

|

ПСА |

x |

x |

x |

1 |

1 |

0 |

x |

x |

F8 |

|

- |

x |

x |

x |

1 |

1 |

1 |

x |

x |

FC |

x – произвольное состояние линии. Условно примем A15=A14=A13=1 и А1=А0=0.

Для выбора микросхем используем дешифратор К555ИД7 [4], построенный на базе логики ТТЛШ. Данный тип логики совместим с уровнями ТТЛ, а значит, и с базой микросхем КР580, но, в отличие от серий ТТЛ (К155, К133) имеет гораздо более низкое энергопотребление и высокое быстродействие.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.