Состояния коммутации 10-15 можно реализовать путём введения на выход шлюзового элемента. В результате аналитическое выражение для состояния на выходе будет иметь структуру:

![]() , где

, где

Kf – минимизированная с безразличными состояниями при запрещённых адресных комбинациях функция коммутации;

Gf – шлюзовая функция; имеет значение 1 на всех допустимых комбинациях на входах адреса и 0 в ином случае.

Определим таблицы истинности для этих функций:

Таблица 14 - Таблица истинности ФАЛ Kf.

|

Десятичный эквивалент адреса |

Состояние адресных входов |

Kf |

|||

|

A1 |

A2 |

A3 |

A4 |

Q |

|

|

0 |

0 |

0 |

0 |

0 |

D0 |

|

1 |

0 |

0 |

0 |

1 |

D1 |

|

2 |

0 |

0 |

1 |

0 |

D2 |

|

3 |

0 |

0 |

1 |

1 |

D3 |

|

4 |

0 |

1 |

0 |

0 |

D4 |

|

5 |

0 |

1 |

0 |

1 |

D5 |

|

6 |

0 |

1 |

1 |

0 |

D6 |

|

7 |

0 |

1 |

1 |

1 |

D7 |

|

8 |

1 |

0 |

0 |

0 |

D8 |

|

9 |

1 |

0 |

0 |

1 |

D9 |

|

10 |

1 |

0 |

1 |

0 |

~ |

|

... |

... |

... |

... |

... |

~ |

|

15 |

1 |

1 |

1 |

1 |

~ |

Таблица 15 - Таблица истинности ФАЛ Gf.

|

Десятичный эквивалент адреса |

Состояние адресных входов |

Gf |

|||

|

A1 |

A2 |

A3 |

A4 |

Q |

|

|

0 |

0 |

0 |

0 |

0 |

1 |

|

1 |

0 |

0 |

0 |

1 |

1 |

|

2 |

0 |

0 |

1 |

0 |

1 |

|

3 |

0 |

0 |

1 |

1 |

1 |

|

4 |

0 |

1 |

0 |

0 |

1 |

|

5 |

0 |

1 |

0 |

1 |

1 |

|

6 |

0 |

1 |

1 |

0 |

1 |

|

7 |

0 |

1 |

1 |

1 |

1 |

|

8 |

1 |

0 |

0 |

0 |

1 |

|

9 |

1 |

0 |

0 |

1 |

1 |

|

10 |

1 |

0 |

1 |

0 |

0 |

|

... |

... |

... |

... |

... |

0 |

|

15 |

1 |

1 |

1 |

1 |

0 |

Зададим функции Kf и Gf картами Карно и произведём их минимизацию для ДНФ.

Рисунок 33 - Минимизация функций картами Карно.

Составим минимизированные выражения для функций:

![]()

Преобразуем эти выражения следующим образом с помощью правила де Моргана:

![]()

Реализуем мультиплексор в абстрактных логических элементах (ШMП1 – локальная шина устройства).

|

Рисунок 34 – Заданный мультиплексор (абстрактные элементы). |

Выберем компонентную базу для построения счётчика.

SN74LS30 – 8-ми входовой элемент И-НЕ;

SN74LS22 – два 4-х входовых элемента И-НЕ;

SN74LS00D – четыре 2-х элемента входовых И-НЕ.

Выполним мультиплексор в приведённой выше компонентной базе.

|

Рисунок 35 - Заданный мультиплексор (в компонентной базе). |

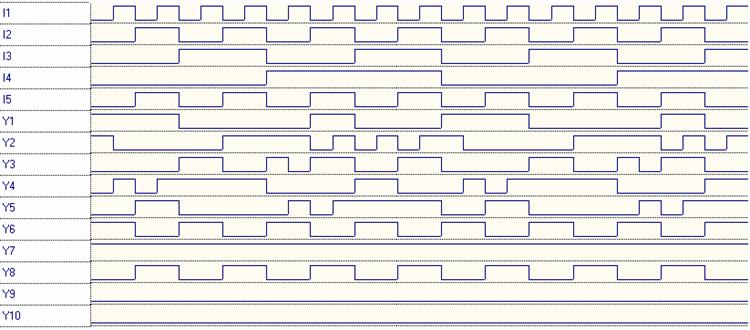

3 Временные диаграммы работы основных блоков устройства

Временные диаграммы показывают зависимости выходных сигналов устройства от того, как изменяются входные сигналы во временной области.

Анализ временных диаграмм позволяет судить о корректности работы того или иного устройства, а также о правильности выполнения возложенных на устройство функций.

Ниже приведены временные диаграммы построенных блоков проектируемого дискретного устройства. В указанных диаграммах не учитывается задержка реакции выхода используемых элементов компонентной базы.

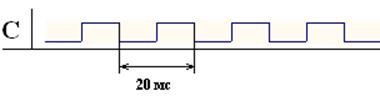

Рисунок 36 – Временная диаграмма работы тактового генератора.

Рисунок 37 – Диаграмма состояний преобразователя кода.

Рисунок 38 – Диаграмма состояний мультиплексора.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.