Алгоритмическое описание электрической централизации должно обеспечивать ее функциональную безопасность U = {Uk}, k = 1, 2,…7 (см. раздел 2.1.5) при выполнении всех технологических операций по движению поездов и маневровой работе на станции.

В основу разработки алгоритмов положен системный принцип «сверху—вниз», т. е. от общих проблем к конкретным деталям. Это объясняется тем, что даже для относительно простых систем ЭЦ трудно разработать алгоритм, охватывающий все детали их функционирования. Поэтому целесообразно разрабатывать алгоритмы, имевшие разные последовательные уровни детализации. При разработке устройств на релейно-контактных элементах можно выделить два основных уровня детализации: концептуальную и функциональную блок-схемы алгоритма. При разработке систем, использующих вычислительную технику, необходимо к описанным добавить третий уровень – структурную схему машинных команд.

Концептуальная блок-схема алгоритма содержит общие положения (требования), показывающие, что именно должно быть сделано. Она разрабатывается в виде связанного набора крупных модулей, определяющих принцип действия системы ЭЦ или ее отдельного устройства. Функциональная блок-схема алгоритма показывает, как должна быть выполнена система. Эта схема представляет собой детализацию модулей концептуальной схемы, причем степень такой детализации также может быть различной в зависимости от требуемой точности. Структурная схема алгоритма – это детальная схема, представляющая собой указатель для кодирования команд в выбранном вычислительном комплексе.

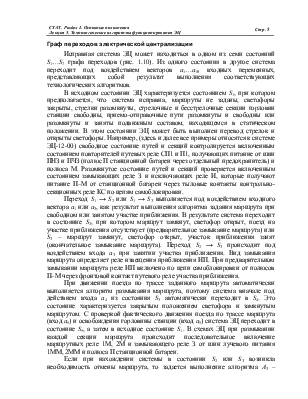

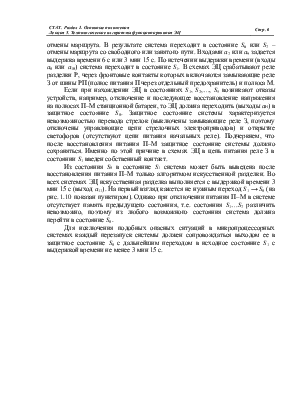

Обычно используется графическое представление алгоритмов в виде блок-схем, на которых все выполняемые операции подразделяются на функциональные и логические. Кроме того, каждый алгоритм должен иметь операторы «Начало» и «Конец», а для частей общего алгоритма – операторы «Вход» и «Выход». Функциональные операторы < ФО > осуществляют непосредственное преобразование информации, логические операторы < ЛО > определяют направление выполнения операторов алгоритма. На схеме < ФО > изображаются в виде прямоугольника с одним входом и одним выходом. Внутри прямоугольника записывается краткая характеристика действия данного < ФО > на языке, близком к естественному. Логические операторы < ЛО > изображаются ромбом, внутри которого также записывается его характеристика; < ЛО > имеют один вход и два выхода, на линиях которых записывается «Да», когда условие выполняется, и «Нет», если условие не выполняется.

В качестве примера рассмотрим детализацию фрагмента функциональной блок-схемы алгоритма (рис. 1.3, а) выключения замыкающего реле (оператор < ФО2 >) при срабатывании сигнального реле I каскада < ФО1 > в ЭЦ промежуточных станций. На втором уровне детализации (рис. 1.3, б) операторами < ФО11 > … < ФО11 > и < ФО21 > … < ФО23 > учитываются коммутация тока в обмотках реле, а также работа их контактных систем. Если необходимо, например при моделировании схемы, учесть временные параметры реле, то дальнейшая детализация (рис. 1.3, в) предусматривает посредством < ЛО12 > ввод временной задержки (включение таймера

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.