Кодер данного сверточного кода выполняется по схеме РС за исключением того, что блок разделения проверочных и информационных символов заменяется блоком сложения и располагается на выходе РС.

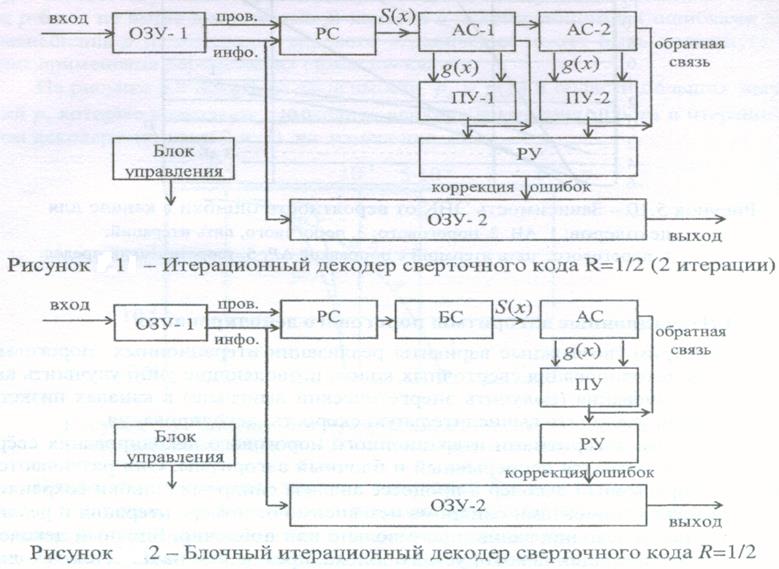

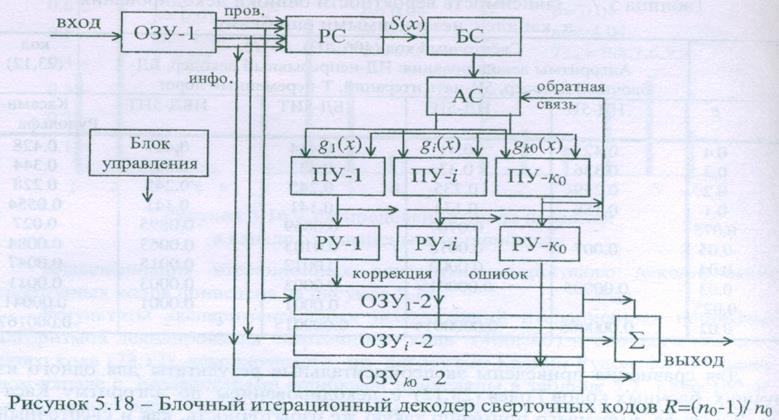

Скорость работы непрерывного декодера (рисунок 5.11), когда длина декодируемого блока равна длине кадра n0, практически ограничивается только быстродействием элементной базы. Если длина блока больше длины кадра, предельная скорость работы декодера снижается из-за необходимости записи и считывания блоков; ещё ниже скорость работы блочных декодеров (рисунок 5.12), когда используется один анализатор синдрома (АС). Однако, когда декодер реализуется программно на микропроцессорах или микро-ЭВМ (например, встроенный декодер), блочный декодер может оказаться предпочтительнее. Процесс сдвига в регистрах может быть заменён сканированием только тех ячеек памяти, в которых выполняется операция суммирования по модулю два, что позволяет существенно уменьшить вычислительную сложность декодера (число операций на один декодируемый символ кода), а значит увеличить скорость его работы.

При этом вычислительная сложность декодера может быть определена как

Фk(j) =Сk1*к*j(у+1)+Сk2, (5.43)

где Сk1 - коэффициент пропорциональности. Сk2 - постоянная, определяемая типом ЭВМ.

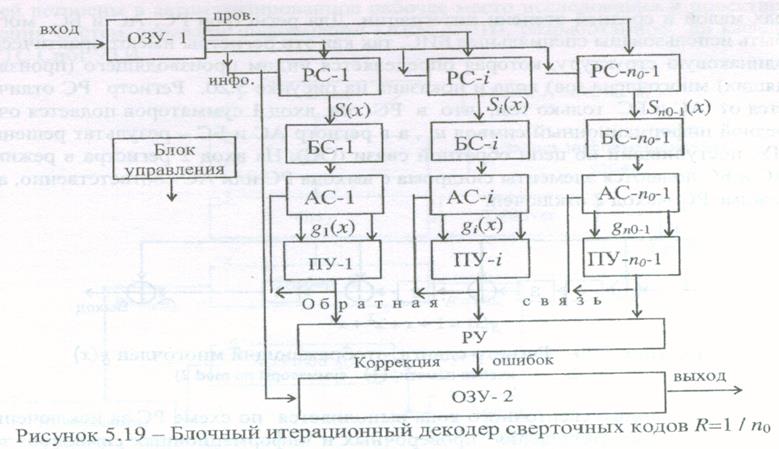

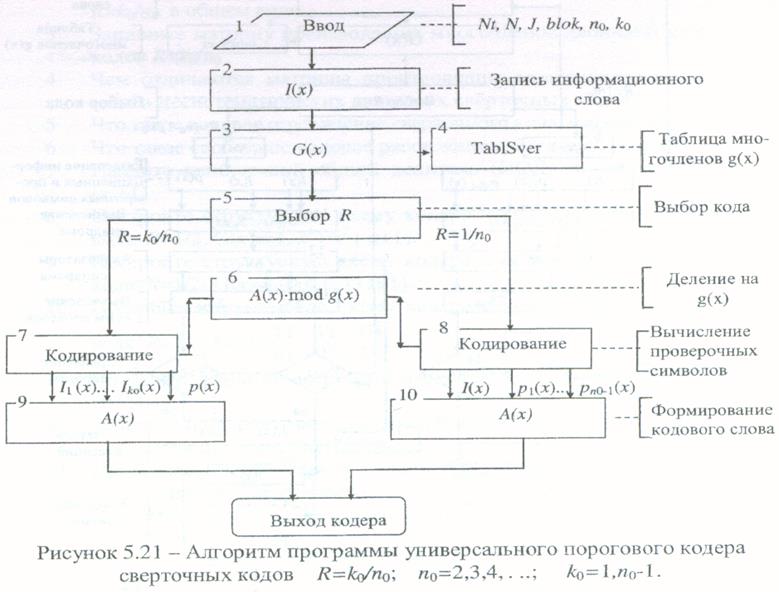

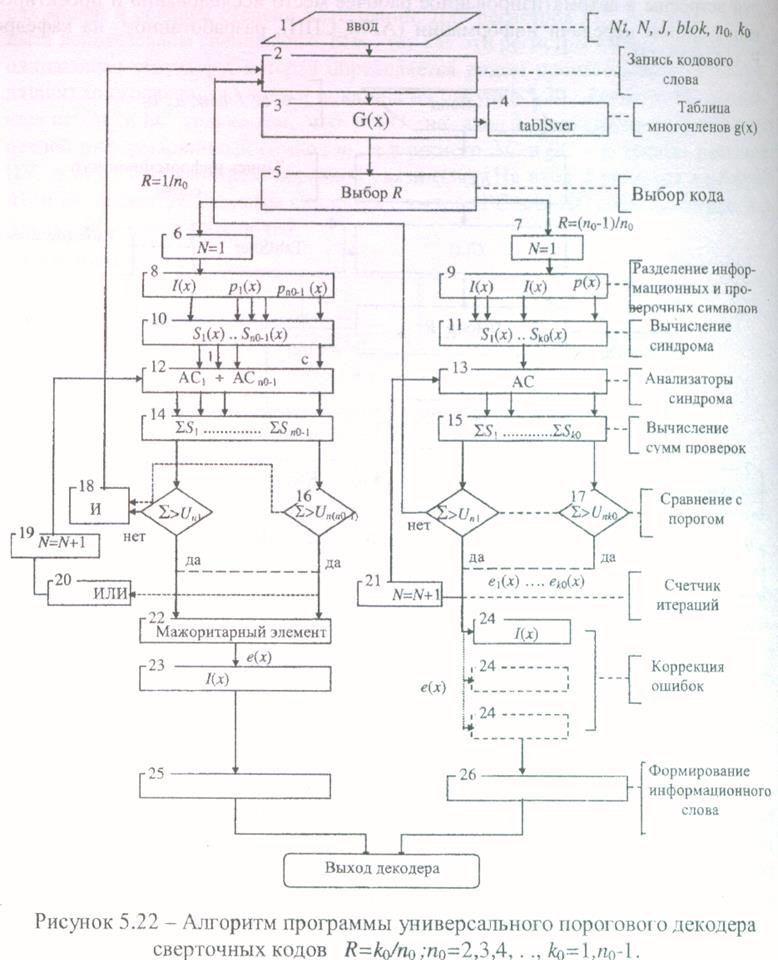

Алгоритмы программного обеспечения для реализации универсального кодера сверточных кодов R=k0/n0, n0=2,3,4,5 . ., kо=1,nо-1 и блочного итерационного порогового декодера на ЭВМ показаны, соответственно, на рисунках 5.21 и 5.22.

Блоки 1 алгоритмов предполагают ввод параметров кода (k0, по , номеров порождающих многочленов из таблицы, установку начала блока и начала итераций. В блоках 2 происходит запись кодируемого и декодируемого слов; блоки 3, 4 считывают заданные порождающие многочлены из указанной выше таблицы; затем в блоках 5 производится выбор направления ал! оритма в зависимости от скорости кода (k0= 1 или k0 =по-1).

Далее в кодере производится вычисление проверочных символов и формирование выходной последовательности символов.

В алгоритме декодера выполняются те же операции, что и в структурных схемах декодеров, показанных на рисунках 5.18 и 5.19: разделение декодируемой последовательности на информационные и проверочные символы (блоки 8, 9), вычисление синдрома ошибок (блоки 10, 11), анализ синдрома (блоки 12, 13), сравнение суммы элементов синдрома с порогом (блоки 14, 15, 16, 17), коррекция ошибок (блоки 22, 23, 24), формирование информационной последовательности на выходе (блоки 25, 26).

В алгоритме декодера дополнительно введены: "счетчик числа итераций": блоки 19 и 21 с проверкой максимального числа итераций. Максимальное число итераций выбрано равным 6 (при этом среднее число итераций в реальном канале может быть равно 1.1-1,5), так как при плохом качестве канала в пороговых декодерах с обратной связью возможно размножение ошибок и их исправление становится невозможным при любом числе итераций.

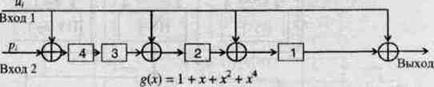

Рисунок 5.20 - Регистр сдвига, отображающий многочлен g(х) (1,2,3,4 - ячейки памяти, +- сумматоры по тоd 2)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.