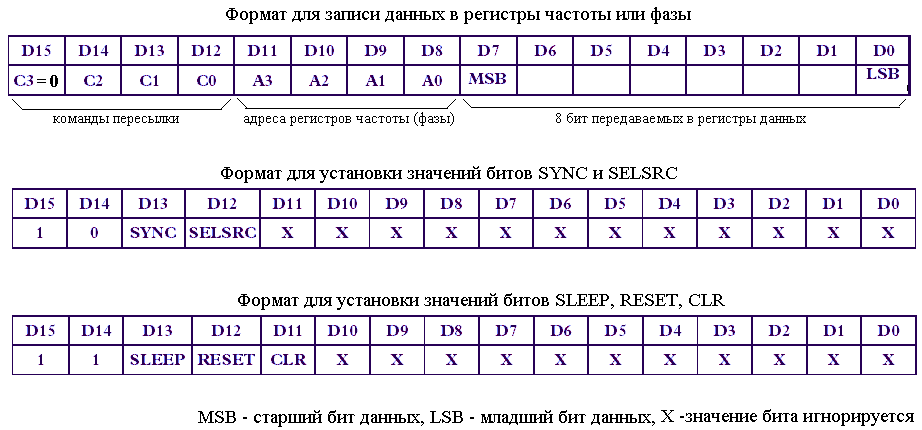

Опишем теперь порядок загрузки регистров и записи команд синтезатора AD9832. Протокол обмена данными, принятый в синтезаторе, предусматривает передачу данных и команд 16-битными словами D15…D0 (рис. 4.3), в которых предусмотрены:

- биты для передачи команд С3…С0 (это команды пересылки данных в регистры синтезатора);

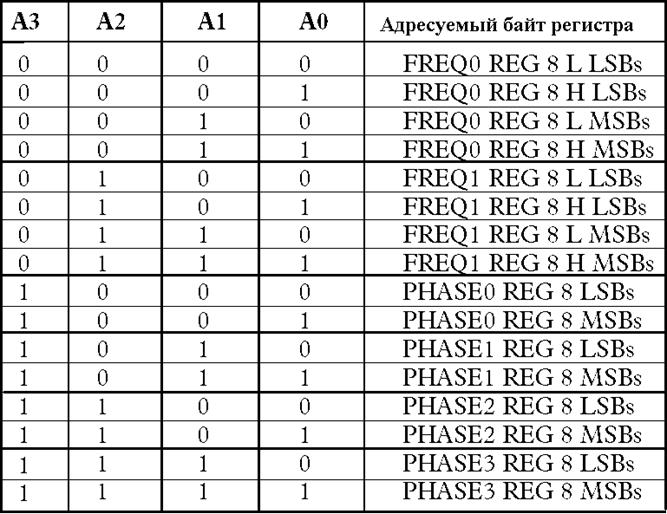

- биты А3…А0 адреса регистра фазы или частоты, в который отправляют данные (табл. 4.1);

- биты данных о частоте или фазе MSB…LSB (8 бит);

- команды для установки значений битов SYNC, SELSRC (их значение см. выше);

- команды для установки значений битов SLEEP, RESET, CLR.

SLEEP = 1 - режим пониженного энергопотребления микросхемы, выходной сигнал отсутствует («спящий» режим); SLEEP = 0 – обычный рабочий режим.

RESET = 1 – сброс аккумулятора фазы, на выходе синтезатора присутствует ток, равный половине полного значения токовой шкалы; RESET = 0 – обычный рабочий режим.

CLR = 1 – сброс битов SYNC, SELSRC в ноль. Бит CLR после установки пользователем в 1 автоматически возвращается в 0 (в отличие от битов SLEEP и RESET).

Рис. 4.3

Рис. 4.4

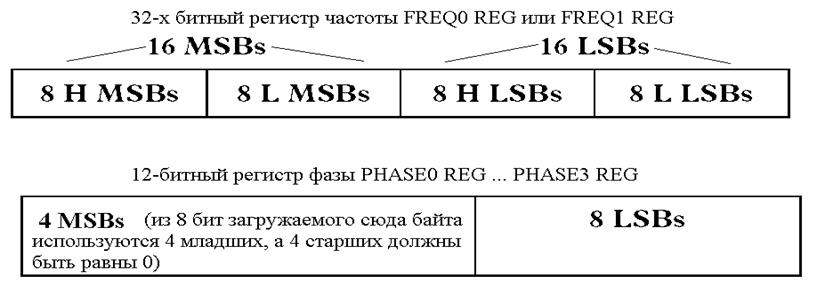

Из рис. 4.3, в частности, видно, что передать в какой-либо регистр частоты или фазы можно за один цикл обращения к ИМС синтезатора только 8 бит данных. Поэтому 32-х битные регистры частоты FREQ0 REG и FREQ1 REG разделены на 4 байта, а 12-битные регистры фазы PHASE0 REG…PHASE3 REG –на 2 байта, как это показано на рис. 4.4. Адреса каждого из этих байтов приведены в табл. 4.1.

Список команд, управляющих загрузкой данных в регистры частоты и фазы, приведен в табл. 4.2. Из этой таблицы ясно, что данные через последовательный порт синтезатора поступают порциями в один байт, а в регистры частоты или фазы загружаются двухбайтными словами, поскольку байт, переданный первым, дожидается следующего байта в промежуточном 16-битном регистре DEFER REGISTER, который можно увидеть на рис. 4.2.

Таким образом, чтобы загрузить 12-разрядный регистр фазового сдвига PHASEi REG, достаточно одной пересылки из промежуточного регистра DEFER REGISTER, а для загрузки регистра частоты необходимо две таких пересылки.

Приведем пример последовательности команд для установления частоты синтезатора. Пусть необходимо в качестве рабочего регистра выбрать FREQ1 регистр и установить частоту f OUT = 1,1234567 МГц при тактовой частоте f MCLK = 25 МГц. Выбор рабочего регистра частоты пусть производится программным способом (SELSRC = 1).

1) Выводим синтезатор из спящего режима, устанавливаем бит SELSRC = 1 (как это сделать – см. рис. 4.3). На входе FSELECT нужно установить логический 0.

2) Указываем в качестве рабочего регистра FREQ1 REG, для чего отправляем в синтезатор команду D15…D0 = 0101 1 00000000000, см. табл. 4.2 и рис. 4.3.

3) Находим содержание байтов 8H MSBs…8L LSBs (рис.4.4), используя встроенный калькулятор Windows:

8H MSBs = 00001011; 8L MSBs = 10000001;

8H LSBs = 00010011; 8L LSBs = 00000111.

4) Записываем 8 бит частоты в DEFER REGISTER, начиная с самого старшего байта 8H MSBs (что не обязательно). Для этого записываем команду D15…D0 = 0011 0111 00001011, см. табл. 4.1, 4.2 и рис. 4.3.

5) Записываем еще 8 бит частоты (это 8L MSBs) и отправляем вместе 8H MSBs и 8L MSBs в регистр FREQ1 REG с помощью команды D15…D0 = 0010 0110 10000001.

6) Аналогично загружаем 8 бит частоты (теперь это 8H LSBs) в DEFER REGISTER: D15…D0 = 0011 0100 00010011.

7) Дописываем последние 8 бит частоты (это 8L LSBs) и отправляем вместе 8H LSBs и 8L LSBs в регистр FREQ1 REG с помощью команды D15…D0 = 0010 0110 00000111.

После этой записи на выходе ИМС появляется колебание с требуемой частотой.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.