- осциллограф - наблюдение формы колебания на выходе синтезатора;

- частотомер – контроль частоты колебания на выходе синтезатора (подключен параллельно осциллографу).

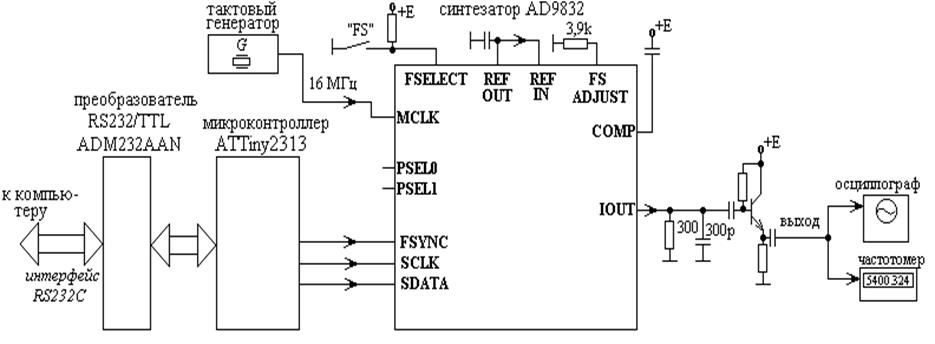

Лабораторный макет синтезатора частоты (структурная схема – рис.4.1) выполнен на основе ИМС прямого цифрового синтезатора частоты (Direct Digital Synthesizer – DDS) AD9832 фирмы «Analog Devices», вырабатывающей ток квазисинусоидальной формы, частота и начальная фаза которого зависят от управляющих битов, записываемых пользователем в память ИМС синтезатора при помощи специальной управляющей программы для персонального компьютера. Токовый сигнал преобразуется в синусоидальное напряжение буферным транзисторным каскадом и подается на измерительные приборы, по которым можно судить о его форме и частоте.

Рис. 4.1

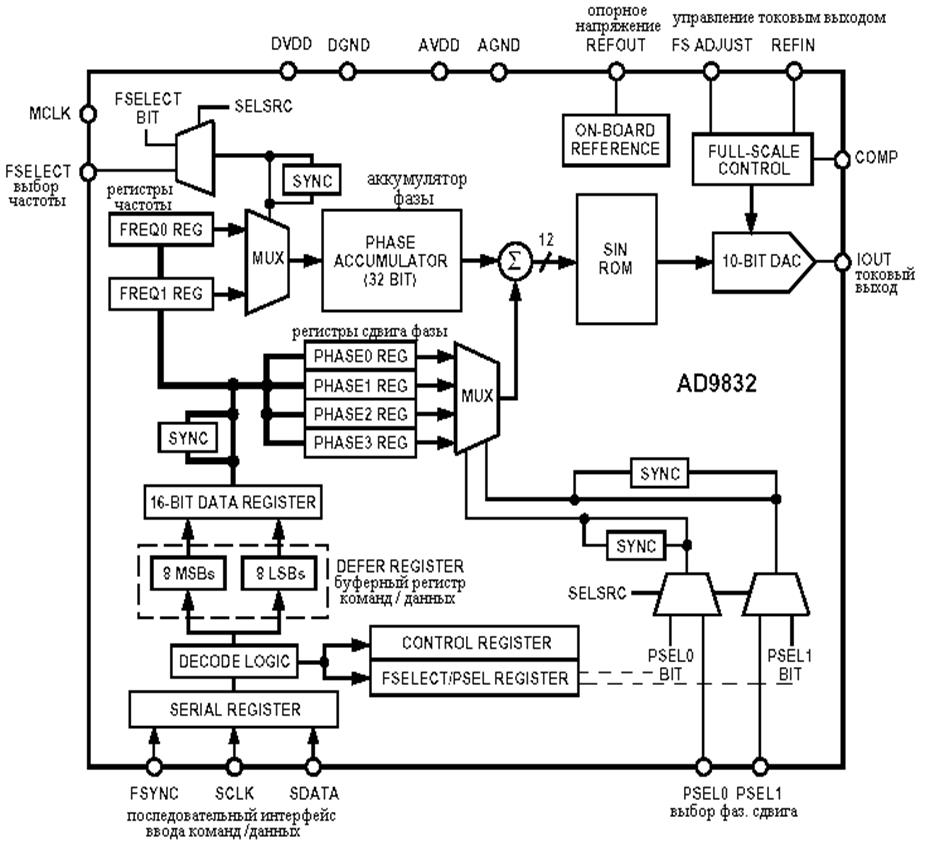

Тактовый сигнал с частотой f MCLK = 16 МГц для ИМС синтезатора вырабатывается монолитным кварцевым генератором и подается на вход MCLK микросхемы. Поскольку микросхема AD9832 обладает 32-разрядным аккумулятором фазы (структуру микросхемы см. на рис. 4.2), то частота выходного колебания синтезатора f OUT будет определяться следующим образом:

f OUT = (f MCLK / 232)*FREQ,

где FREQ – 32-х разрядный (в двоичном представлении) код частоты, записанный в один из регистров частоты FREQ0 REG, FREQ1 REG. Из этой формулы видно, что данный синтезатор способен формировать синусоидальный сигнал в диапазоне частот от сотых долей герца до единиц мегагерц без каких-либо переключений. Все необходимые данные синтезатор получает от компьютера через микроконтроллер ATTiny2313 фирмы ATMEL, в памяти которого находится программа преобразования данных из формата интерфейса RS-232C в специальный формат последовательной передачи данных, встроенный в ИМС AD9832.

Рис. 4.2

Кроме двух 32-разрядных регистров FREQ0 REG и FREQ1 REG, в которых могут храниться коды частоты выходного сигнала, в ИМС синтезатора предусмотрены еще четыре 12-разрядных регистра, в которых могут быть записаны четыре возможных значения начальной фазы выходного сигнала: PHASE0 REG…PHASE3 REG. Регистры выбора частоты и регистры выбора сдвига фазы подключены к фазовому аккумулятору через мультиплексоры (MUX), управляемые одним из двух способов: аппаратно или программно. Способ выбора регистра частоты или начальной фазы задается битом SELSRC прошивки синтезатора:

- SELSRC = 1 - программный выбор, когда за подключение конкретного регистра к фазовому аккумулятору отвечают определенные биты прошивки синтезатора: FSELECT (для частоты) и PSEL0, PSEL1 (для фазового сдвига); нужно помнить, что в режиме программного выбора частоты (фазы) на входе FSELECT (на входах PSEL0, PSEL1) должен быть установлен низкий логический уровень;

- SELSRC = 0 - аппаратный выбор, когда указанные выше биты игнорируются, а выбор регистра зависит от логических уровней на входах ИМС FSELECT (для частоты) и PSEL0, PSEL1 (для фазового сдвига).

Пример:

- установлено FSELECT = 0, следовательно, используется регистр FREQ0 REG;

- установлено PSEL0 = 0, PSEL1 = 0, следовательно, используется регистр PHASE0 REG.

В данном лабораторном макете, как это видно из рис. 4.1, предусмотрено ручное управление только состоянием входа FSELECT, для чего на верхней крышке лабораторного макета установлен тумблер «FS».

Нужно отметить, что смену регистров частоты или фазового сдвига нежелательно производить в моменты положительного фронта тактового сигнала синтезатора, в противном случае возможны искажения выходного сигнала. Для устранения нежелательных последствий таких переключений в ИМС AD9832 предусмотрены подключаемые по желанию пользователя логические блоки синхронизации загрузки «SYNC» (см. рис. 4.2). При установке бита SYNC = 1 включается задержка смены регистров частоты и фазы, необходимая для устранения искажений синусоиды; если же SYNC = 0, смена частоты или фазы происходит асинхронно. Впрочем, для данной лабораторной работы указанное обстоятельство существенного значения не имеет, и бит SYNC может быть установлен произвольно.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.