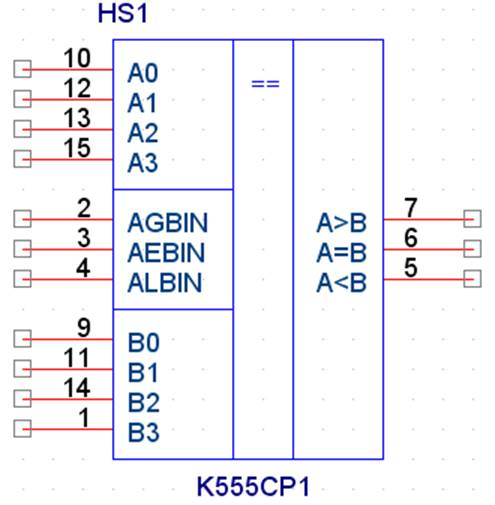

УГО моделируемого узла.

Рис. 32. УГО проектируемого иерархического символа

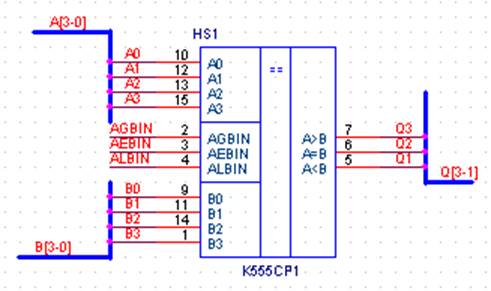

Рис. 33. Принципиальная схема CP1.

В схеме замещения были использованы те же элементы, которые использовались при проектировании в пакете DesignLab 8.0. Как и ранее, созданные модели вентилей не соответствуют реальным элементам по динамическим характеристикам. Ниже приведены VHDL-модели для данных вентилей.

Тиражирование описаний связано с тем, что в одном корпусе ИМС имеется несколько секций. Это процедура необходима, когда в одном корпусе ИМС содержатся элементы с разными функциями.

***********************************Элемент 2И-НЕ*****************************

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY K555LA3 IS PORT(

\A1_-1\ : IN std_logic;

\A1_-2\ : IN std_logic;

\A1_-3\ : IN std_logic;

\A1_-4\ : IN std_logic;

\B1_-1\ : IN std_logic;

\B1_-2\ : IN std_logic;

\B1_-3\ : IN std_logic;

\B1_-4\ : IN std_logic;

\Y1_-1\ : OUT std_logic;

\Y1_-2\ : OUT std_logic;

\Y1_-3\ : OUT std_logic;

\Y1_-4\ : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic);

END K555LA3;

ARCHITECTURE model OF K555LA3 IS

BEGIN

\Y1_-1\ <= NOT ( \A1_-1\ AND \B1_-1\ ) AFTER 1 ns;

\Y1_-2\ <= NOT ( \A1_-2\ AND \B1_-2\ ) AFTER 1 ns;

\Y1_-3\ <= NOT ( \A1_-3\ AND \B1_-3\ ) AFTER 1 ns;

\Y1_-4\ <= NOT ( \A1_-4\ AND \B1_-4\ ) AFTER 1 ns;

END model;

********************************Элемент 2ИЛИ-НЕ*****************************

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY K555LE1 IS PORT(

\A5_-1\ : IN std_logic;

\A5_-2\ : IN std_logic;

\A5_-3\ : IN std_logic;

\A5_-4\ : IN std_logic;

\B5_-1\ : IN std_logic;

\B5_-2\ : IN std_logic;

\B5_-3\ : IN std_logic;

\B5_-4\ : IN std_logic;

\Y5_-1\ : OUT std_logic;

\Y5_-2\ : OUT std_logic;

\Y5_-3\ : OUT std_logic;

\Y5_-4\ : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic);

END K555LE1;

ARCHITECTURE model OF K555LE1 IS

BEGIN

\Y5_-1\ <= NOT ( \A5_-1\ OR \B5_-1\ ) AFTER 1 ns;

\Y5_-2\ <= NOT ( \A5_-2\ OR \B5_-2\ ) AFTER 1 ns;

\Y5_-3\ <= NOT ( \A5_-3\ OR \B5_-3\ ) AFTER 1 ns;

\Y5_-4\ <= NOT ( \A5_-4\ OR \B5_-4\ ) AFTER 1 ns;

END model;

***********************************Элемент 2И********************************

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY K555LI1 IS PORT(

\A2_-1\ : IN std_logic;

\A2_-2\ : IN std_logic;

\A2_-3\ : IN std_logic;

\A2_-4\ : IN std_logic;

\B2_-1\ : IN std_logic;

\B2_-2\ : IN std_logic;

\B2_-3\ : IN std_logic;

\B2_-4\ : IN std_logic;

\Y2_-1\ : OUT std_logic;

\Y2_-2\ : OUT std_logic;

\Y2_-3\ : OUT std_logic;

\Y2_-4\ : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic);

END K555LI1;

ARCHITECTURE model OF K555LI1 IS

BEGIN

\Y2_-1\ <= ( \A2_-1\ AND \B2_-1\ ) AFTER 1 ns;

\Y2_-2\ <= ( \A2_-2\ AND \B2_-2\ ) AFTER 1 ns;

\Y2_-3\ <= ( \A2_-3\ AND \B2_-3\ ) AFTER 1 ns;

\Y2_-4\ <= ( \A2_-4\ AND \B2_-4\ ) AFTER 1 ns;

END model;

******************************Элемент 2И (на выходах)**************************

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY KR1533LI1 IS PORT(

\A_-1\ : IN std_logic;

\A_-2\ : IN std_logic;

\A_-3\ : IN std_logic;

\A_-4\ : IN std_logic;

\B_-1\ : IN std_logic;

\B_-2\ : IN std_logic;

\B_-3\ : IN std_logic;

\B_-4\ : IN std_logic;

\Y_-1\ : OUT std_logic;

\Y_-2\ : OUT std_logic;

\Y_-3\ : OUT std_logic;

\Y_-4\ : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic);

END KR1533LI1;

ARCHITECTURE model OF KR1533LI1 IS

SIGNAL AND2_1 : std_logic;

SIGNAL AND2_2 : std_logic;

SIGNAL AND2_3 : std_logic;

SIGNAL AND2_4 : std_logic;

begin

process(\A_-1\,\B_-1\,\Y_-1\,AND2_1) begin

AND2_1<=(\A_-1\and\B_-1\);

if (AND2_1'EVENT) then -- проверка на переключение сигналов

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.