|

I0вх, мА, не более: по входам: А>В и А<В по остальным входам |

0,38 1,14 |

|

I1вх, мА, не более: по входам: А>В и А<В по остальным входам |

0,01 0,03 |

|

U0вых, В, не менее |

0,48 |

|

U1вых, В, не менее |

2,6 |

|

Iпот, мА, не более |

19,5 |

|

tзд.р 1->0, нс, от входов А,B к выходу А<В от входов A,В к выходу А>В от входов A,В к выходу А=В от входа АGBIN к выходу А<В от входов ALBIN к выходу А>В от входов AEBIN к выходу А=В |

30 |

|

tзд.р 0->1, нс, от входов А,B к выходу А<В от входов A,В к выходу А>В от входов A,В к выходу А=В от входа АGBIN к выходу А<В от входов ALBIN к выходу А>В от входов AEBIN к выходу А=В |

36 |

Табл. 3. Таблица параметров СП1.

Вся информация относительно параметров и характеристик взята из источника [1].

Микросхема СП1 – схема сравнения двух четырехразрядных чисел. Результатом сравнения является обнаружение одного из трех возможных состояний: А<В, А=В, А>В. Критерием равенства двух двоичных чисел является совпадение их по всем разрядам. Выход схемы сравнения установлен в высокое состояние, если два числа равны, в противном случае выход находится в низком состоянии.

Микросхема имеет четыре сравниваемых входа чисел А и В (А0, В0, А1, В1, А2, В2, А3, В3) и три дополнительных входа переноса А<В, А=В, А>В для сравнения чисел большей разрядности путем последовательного соединения компараторов в каскад, то есть предназначена для построения n-разрядных компараторов в двоичном коде.

Состояния схемы СП1 приведены в табл. 2.

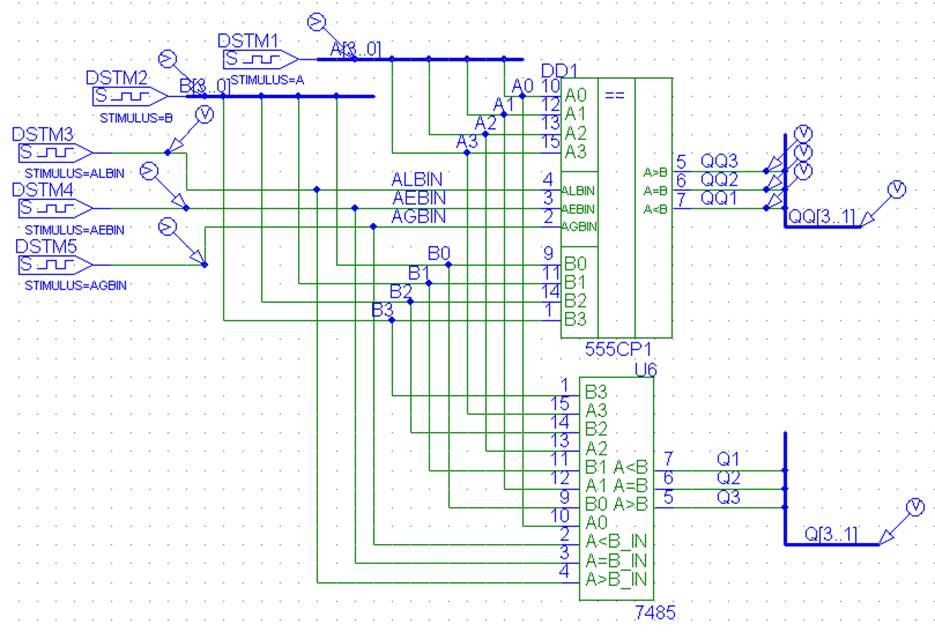

Рис. 2. Принципиальная схема СП1, верификация с зарубежным аналогом.

При создании схемы замещения использовались зарубежные элементы из системной библиотеки 7400.slb, которые были преобразованы в соответствии с принятым ГОСТом и сохранены в личную библиотеку MY_LIB.slb. В функциональных описаниях элементов (файл LIB.mod) пришлось заменить наименования элементов и имена входных и выходных портов. Что же касается задержек распространения, то здесь я оказалась в затруднительном положении из-за сложности схемы. Очень сложно было подобрать задержки элементов таким образом, чтобы суммарные временные задержки были равны табличным. Поэтому я задала задержки таким образом, чтобы суммарные приблизительно равнялись табличным, хотя неточность осталась.

*---------------------------------Элемент 2И-НЕ----------------------------------------

* K555LA3 Quadruple 2-input Positive-Nand Gates

* The TTL Data Book, Vol 2, 1985, TI

* tdn 06/23/89 Update interface and model names

*

.subckt K555LA3 A1 B1 Y1

+ optional: DPWR=$G_DPWR DGND=$G_DGND

+ params: MNTYMXDLY=0 IO_LEVEL=0

U1 nand(2) DPWR DGND

+ A1 B1 Y1

+ D_LA3 IO_STD MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

.ends

*

.model D_LA3 ugate (

+ tplhty=1ns tplhmx=1ns

+ tphlty=1ns tphlmx=1ns

+ )

*$

*-----------------------------------Элемент 2И--------------------------------------

* K555LI1 Quadruple 2-input Positive-And Gates

* The TTL Data Book, Vol 2, 1985, TI

* tdn 06/23/89 Update interface and model names

*

.subckt K555LI1 A2 B2 Y2

+ optional: DPWR=$G_DPWR DGND=$G_DGND

+ params: MNTYMXDLY=0 IO_LEVEL=0

U1 and(2) DPWR DGND

+ A2 B2 Y2

+ D_LI1 IO_STD MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

.ends

*

.model D_LI1 ugate (

+ tplhty=1ns tplhmx=1ns

+ tphlty=1ns tphlmx=1ns

+ )

*$

*-----------------------------------Элемент 2И (на выходах схемы)--------------------------------------

* KR1533LI1 Quadruple 2-input Positive-And Gates

* The TTL Data Book, Vol 2, 1985, TI

* tdn 06/23/89 Update interface and model names

*

.subckt KR1533LI1 A B Y

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.