+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD10_1 B1 $N_0008 $N_0045 $N_0044 $N_0017 $G_DPWR $G_DGND K555LA1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB25_DD6_4 B0 $N_0027 $N_0028 $G_DPWR $G_DGND K555LA3 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB25_DD11_1 $N_0045 $N_0044 $N_0042 $N_0029 $G_DPWR $G_DGND

+ K555LA4 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB25_DD8_2 $N_0028 $N_0029 $N_0030 $G_DPWR $G_DGND K555LL1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB26_DD12_1 $N_0045 $N_0044 $N_0031 $G_DPWR $G_DGND K555LA3

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB26_DD11_2 $N_0042 $N_0040 AGBIN $N_0032 $G_DPWR $G_DGND K555LA4

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB26_DD8_3 $N_0031 $N_0032 $N_0033 $G_DPWR $G_DGND K555LL1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB27_DD12_2 $N_0045 $N_0044 $N_0034 $G_DPWR $G_DGND K555LA3

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB27_DD11_3 $N_0042 $N_0040 AEBIN $N_0035 $G_DPWR $G_DGND K555LA4

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB27_DD8_4 $N_0034 $N_0035 $N_0036 $G_DPWR $G_DGND K555LL1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB29_DD12_3 ALBIN $N_0040 $N_0037 $G_DPWR $G_DGND K555LA3 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB29_DD13_1 $N_0044 $N_0042 $N_0045 $N_0038 $G_DPWR $G_DGND

+ K555LA4 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB29_DD14_1 $N_0037 $N_0038 $N_0039 $G_DPWR $G_DGND K555LL1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD10_2 $N_0044 $N_0045 $N_0008 A1 $N_0019 $G_DPWR $G_DGND K555LA1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB28_DD12_4 AEBIN $N_0040 $N_0041 $G_DPWR $G_DGND K555LA3 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB28_DD13_2 $N_0042 $N_0044 $N_0045 $N_0043 $G_DPWR $G_DGND

+ K555LA4 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_HB28_DD14_2 $N_0041 $N_0043 $N_0046 $G_DPWR $G_DGND K555LL1

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD15_1 $N_0015 $N_0018 QQ3 $G_DPWR $G_DGND KR1533LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD15_2 $N_0022 $N_0023 QQ2 $G_DPWR $G_DGND KR1533LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD15_3 $N_0021 $N_0020 QQ1 $G_DPWR $G_DGND KR1533LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_DD1_DD15_4 $N_0042 $N_0040 $N_0023 $G_DPWR $G_DGND KR1533LI1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

Schematic1.stl

- Информация о месте хранения файла с внешними воздействиями, а также времени его создания и версии программы, с помощью которой он создан

* C:\Univer\Modelirovanie\Kurs\DL\Schematic1.stl written on Mon Dec 01 18:31:54 2003

* by Stimulus Editor -- Serial Number: 100617 -- Version 8.0

;!Stimulus Get

;! AGBIN Digital AEBIN Digital ALBIN Digital A Digital B Digital

;!Ok

;!Plot Axis_Settings

;!Xrange 0s 2us

;!AutoUniverse

;!XminRes 1ns

;!YminRes 1n

;!Ok

.STIMULUS AGBIN STIM (1, 1) **Описаниисигнала AGBIN

+ +0s 0

+ 1.182us 1

+ 1.338us 0

+ 1.607us 1

+ 1.793us 0

.STIMULUS AEBIN STIM (1, 1) **Описаниисигнала AEBIN

+ +0s 0

+ 1.338us 1

+ 1.607us 0

.STIMULUS ALBIN STIM (1, 1) **Описаниисигнала ALBIN

+ +0s 0

+ 1.024us 1

+ 1.182us 0

+ 1.466us 1

+ 1.793us 0

.STIMULUS A STIM (4, 1111) ;! Hex **Описаниисигнала A

+ +0s 1001

+ 143ns 0101

+ 286ns 0100

+ 363ns 0010

+ 508ns 0111

+ 598ns 0100

+ 712ns 0111

+ 842ns 0110

+ 1.024us 0010

+ 1.182us 0101

+ 1.338us 1000

+ 1.466us 0011

+ 1.607us 1101

+ 1.793us 0000

.STIMULUS B STIM (4, 1111) ;! Hex **Описаниисигнала B

+ +0s 0010

+ 143ns 1011

+ 286ns 0010

+ 363ns 0101

+ 508ns 0100

+ 598ns 0111

+ 712ns 0110

+ 842ns 0111

+ 1.024us 0010

+ 1.182us 0101

+ 1.338us 1000

+ 1.468us 0011

+ 1.607us 1101

+ 1.793us 0000

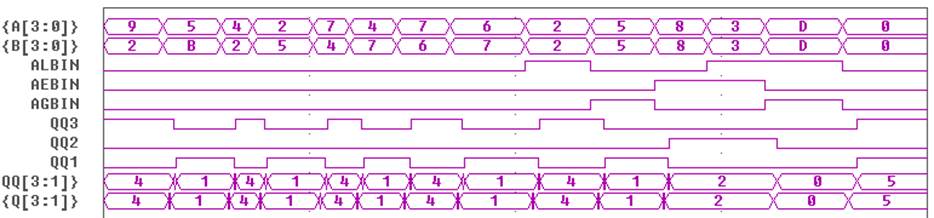

Рис. 5. График из постпроцессора моделирования.

Так как необходимо было реализовать достаточно много (14) состояний цифрового компаратора, то время моделирования пришлось увеличить до 2000 ns. Для ясности оговорюсь что QQ3 – A>B, QQ2 – A=B, QQ1 – A<B.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.