Рассматривая ВД представленную на рис. 49, можно отметить правильность логического функционирования элемента. Временные задержки соответствуют табличным (см. табл. 3).

Далее продемонстрированы непосредственно различные временные задержки проектируемого узла.

![]()

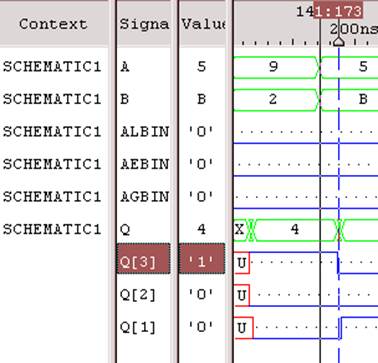

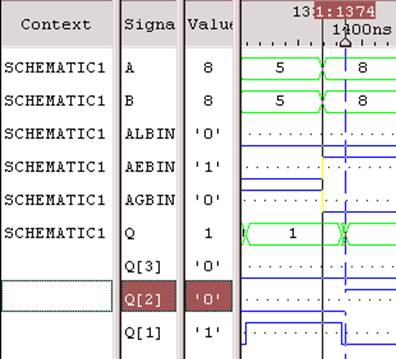

Рис. 50. Задержка распространения сигнала от входов А,В выходу QQ3(A>B) при переключении из 1 в 0 – 30 нс.

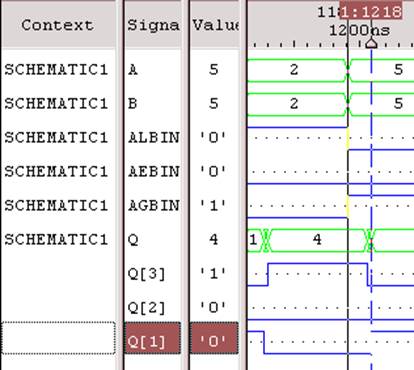

![]()

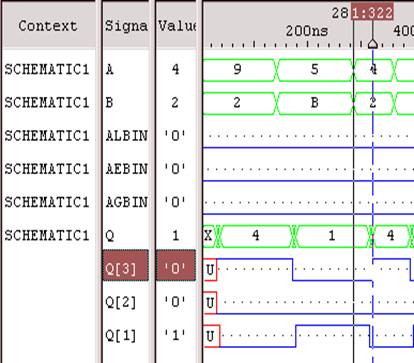

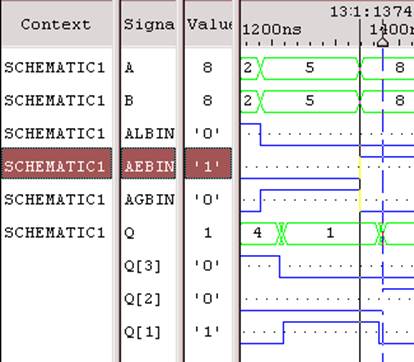

Рис. 51. Задержка распространения сигнала от входов А,В выходу QQ3(A>B) при переключении из 0 в 1 –36 нс.

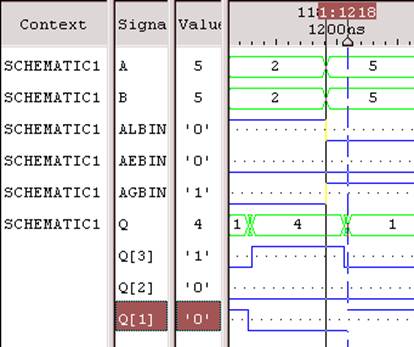

![]()

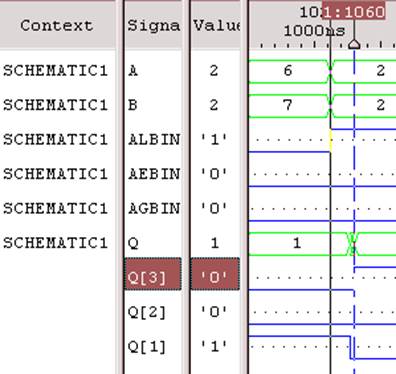

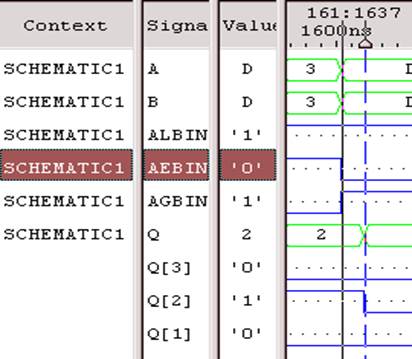

Рис. 52. Задержка распространения сигнала от входа ALBIN выходу QQ3(A>B) при переключении из 0 в 1 –36 нс.

![]()

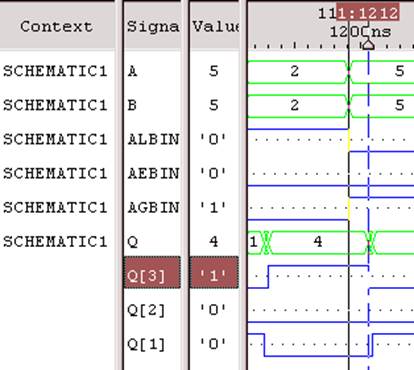

Рис.53. Задержка распространения сигнала от входа ALBIN выходу QQ3(A>B) при переключении из 1 в 0 –30 нс.

![]()

Рис. 54. Задержка распространения сигнала от входов A,B выходу QQ1(A<B) при переключении из 0 в 1 –36 нс.

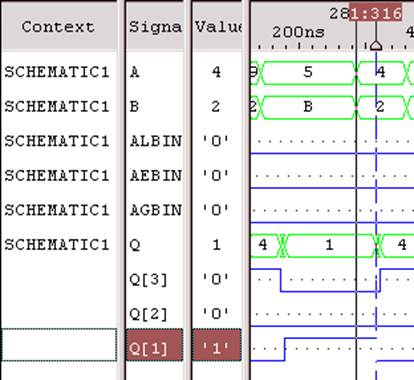

![]()

Рис. 55. Задержка распространения сигнала от входов A,B выходу QQ1(A<B) при переключении из 1 в 0 –30 нс.

![]()

Рис. 56. Задержка распространения сигнала от входа AGBIN выходу QQ1(A<B) при переключении из 0 в 1 –36 нс.

![]()

Рис. 57. Задержка распространения сигнала от входа AGBIN выходу QQ1(A<B) при переключении из 1 в 0 –30 нс.

![]()

Рис. 58. Задержка распространения сигнала от входов A,B выходу QQ2(A=B) при переключении из 0 в 1 –36 нс.

![]()

Рис. 59. Задержка распространения сигнала от входов A,B выходу QQ2(A=B) при переключении из 1 в 0 –30 нс.

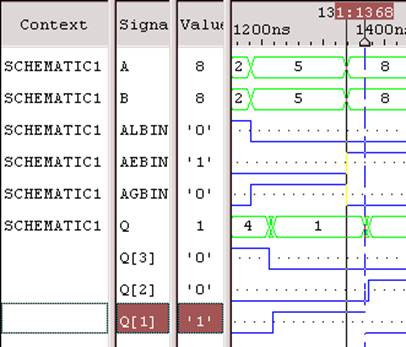

![]()

Рис. 60. Задержка распространения сигнала от входа AЕBIN выходу QQ2(A=B) при переключении из 0 в 1 –36 нс.

![]()

Рис. 61. Задержка распространения сигнала от входа AЕBIN выходу QQ2(A=B) при переключении из 1 в 0 –30 нс.

Теперь можно сказать, что все поставленные перед проектировщиком задачи успешно выполнены. Это обстоятельство подтверждается правильностью функционирования разработанного узла

Целью данной курсовой работы явилось создание функциональной и структурной модели узла в двух пакетах DesignLab 8.0 и OrCAD 9.1. По результатам работы можно провести сравнительный анализ двух пакетов в плане легкости их изучения и использования для создания, тестирования и отладки моделей цифровых устройств.

Работа с пакетом DesignLab 8.0 мне показалась достаточно легкой. Это объясняется тем, что на его изучение на лабораторных работах было затрачено значительно больше времени, чем на OrCAD 9.1. Необходимо было лишь пару раз заглянуть в методические указания и восстановить в памяти изученный материал. Пакет OrCAD 9.1. В моей памяти сохранился очень плохо. Поэтому пришлось постараться за минимальное время освоить его. Теперь, после работы с обоими пакетами можно сделать выводы относительно их изучения, удобства и легкости в обращении.

«Плюсы» и «минусы», которые я выявила при работе с пакетом DesignLab 8.0.

На самом деле достоинств у этого пакета не так уж много. Но несколько я назову.

На этом «плюсы» заканчиваются. Теперь «минусы».

1. Много времени отнимает подключение библиотек.

2. Очень запутанная система создания собственных символов – скопировать АКО-name, скопировать элемент, переименовать элемент, скопировать упаковочную информацию, переименовать её, отредактировать. Куча действий для одного элемента. А у меня их оказалось аж 8 штук! В OrCAD’e это сделано много изящнее и быстрее.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.