![]()

![]()

Рис. 45. Задержка tPHL от

SELECTдля

![]() (40ns) Рис. 46. Задержка tPLH отSELECT для

(40ns) Рис. 46. Задержка tPLH отSELECT для![]()

и

tPLH от

SELECTдля

![]() (27ns) . (27

ns) и tPHL от

SELECT для

(27ns) . (27

ns) и tPHL от

SELECT для ![]() (40 ns).

(40 ns).

![]()

![]()

Рис. 47. Задержка tPHL от

SELECTдля

![]() (40ns) Рис. 48. Задержка tPLH отSELECT для

(40ns) Рис. 48. Задержка tPLH отSELECT для![]()

и tPLH отSELECT для![]() (27ns) . (27 ns).

(27ns) . (27 ns).

8.5. Поведенческая VHDL-модель узла

LIBRARYieee; --подключение необходимых библиотек

USEieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY \K555ID7M\ IS--описание входов и выходов узла

PORT(

A0 : IN std_logic;

A1 : IN std_logic;

A2 : IN std_logic;

NE1 : IN std_logic;

NE2 : IN std_logic;

E3 : IN std_logic;

N0 : OUT std_logic;

N1 : OUT std_logic;

N2 : OUT std_logic;

N3 : OUT std_logic;

N4 : OUT std_logic;

N5 : OUT std_logic;

N6 : OUT std_logic;

N7 : OUT std_logic);

END \K555ID7M\;

ARCHITECTURE model OF \K555ID7M\ IS

signal S : std_logic_vector(2 downto 0); --вектор, используемый для объединения адресных входов

signalEnable:std_logic; --вектор для объединения входов разрешения

BEGIN

S <= A2&A1&A0; --инициализация

Enable<=not(NE1) and not(NE2) and (E3); --инициализация

PROCESS(Enable,S,N0,N1,N2,N3,N4,N5,N6,N7)

BEGIN

IF(Enable='0')then (N7,N6,N5,N4,N3,N2,N1,N0)<="11111111" after 27NS;--проверка разрешения

elseIF (S="000") thenN0<='0'after 40NS; --выбор выхода в зависимости от поступающих

else N0<='1'after 27NS ; --сигналов SELECT

END if;

IF (S="001") then N1<='0'after 40NS;

else N1<='1'after 27NS ;

END if;

IF (S="010") then N2<='0'after 40NS;

else N2<='1'after 27NS ;

END if;

IF (S="011") then N3<='0'after 40NS;

else N3<='1'after 27NS ;

END if;

IF (S="100") then N4<='0'after 40NS;

else N4<='1'after 27NS ;

END if;

IF (S="101") then N5<='0'after 40NS;

else N5<='1'after 27NS ;

END if;

IF (S="110") then N6<='0'after 40NS;

else N6<='1'after 27NS ;

END if;

IF (S="111") then N7<='0'after 40NS;

else N7<='1'after 27NS ;

END if;

END IF;

END PROCESS;

ENDmodel;

8.6. Схема верификации узла с подключённой VHDL-моделью

Схема верификации иерархического символа с подключенной поведенческой VHDL-моделью представлена на рис. 35.

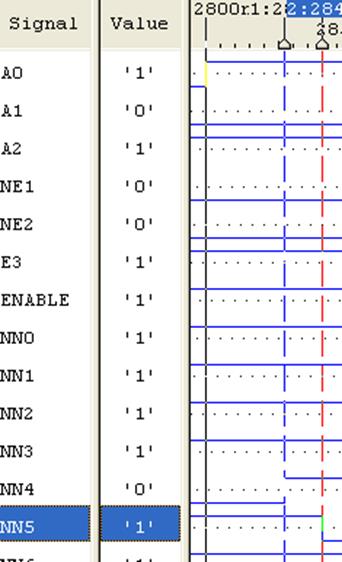

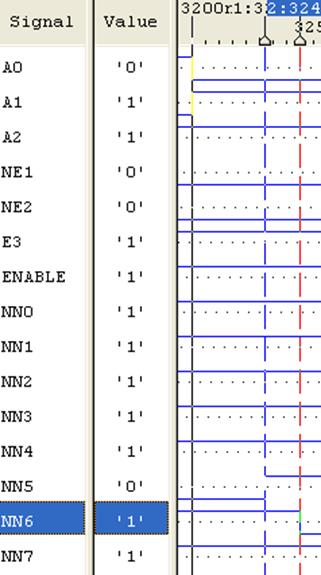

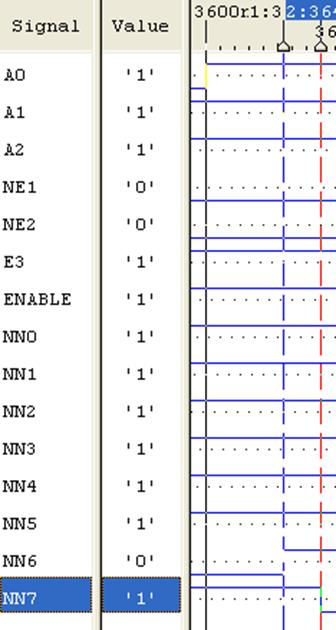

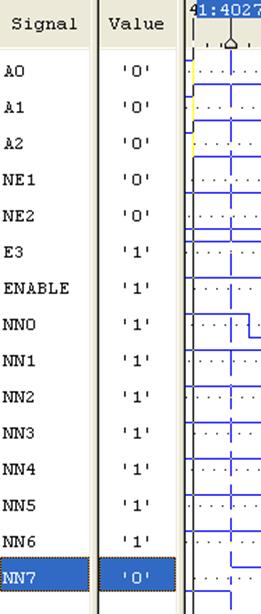

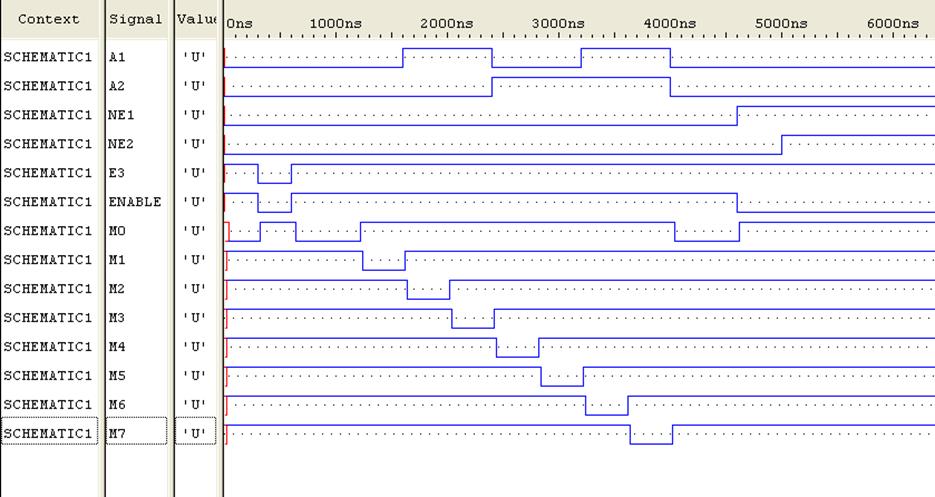

8.7. Результаты верификации поведенческой VHDL-модели узла

Результаты верификации поведенческой модели узла в виде временных диаграмм представлены на рис. 49.

Рис. 49. Результаты моделирования символа с поведенческой VHDL-моделью.

9.1. Макромодель, представленная как иерархический символ

Условное графическое изображение проектируемого узла представлено на рис. 50.

.

Рис. 50. УГО проектируемого узла.

[1] Активное состояние соответствует 0, пассивное состояние – 1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.