Результаты моделирования узла

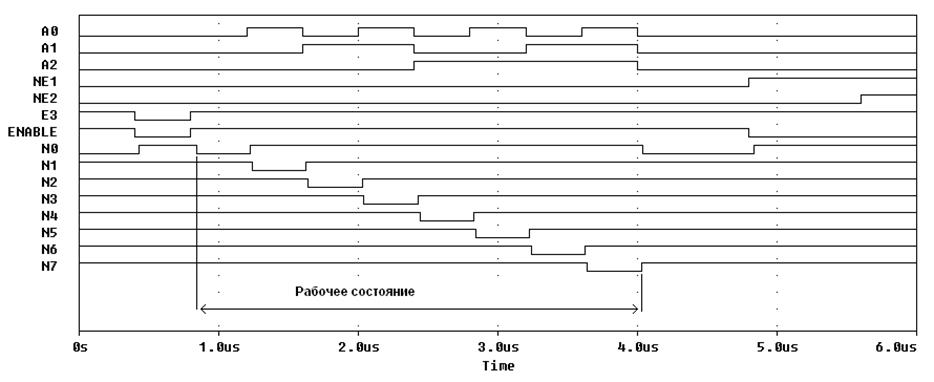

Результаты моделирования узла в виде временных диаграмм представлены на рис. 10.

Рис. 10. Результаты моделирования узла

На временной диаграмме представлены следующие режимы работы узла: Enable = 0, дешифратор выключен (0 – 400 ns, 4.8 - 6 us). При подаче на Enable единицы, DC переходит в рабочий режим (840 – 4027ns), переключая адреса и соответствующие им выходы.

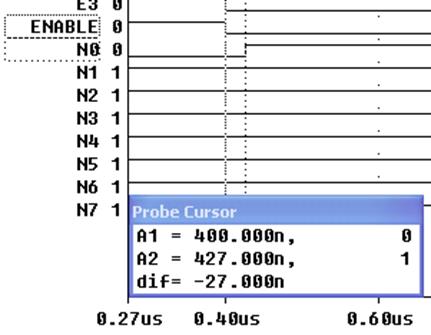

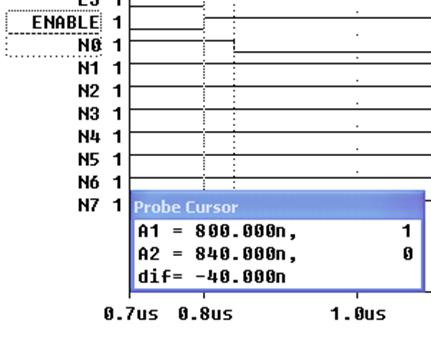

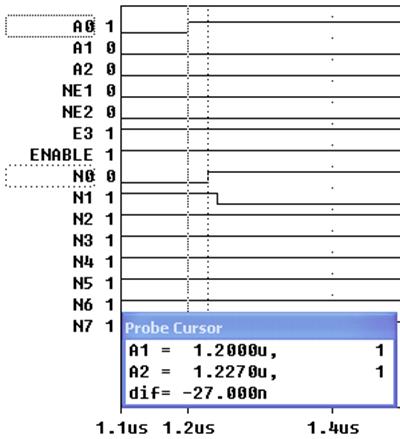

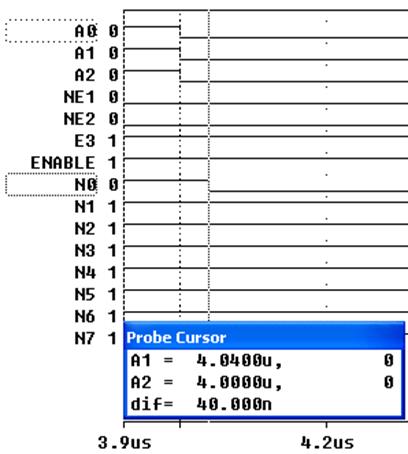

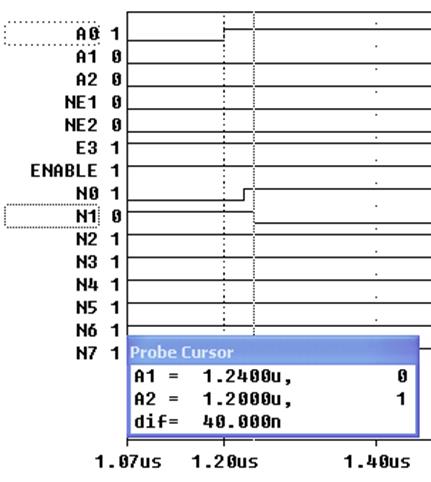

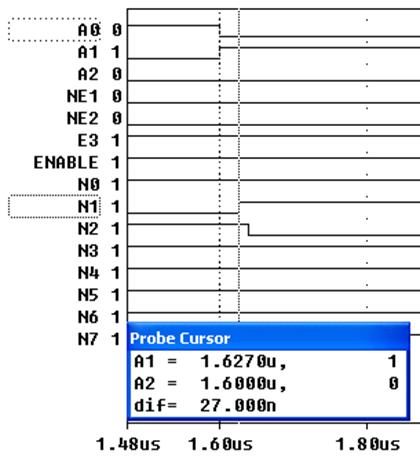

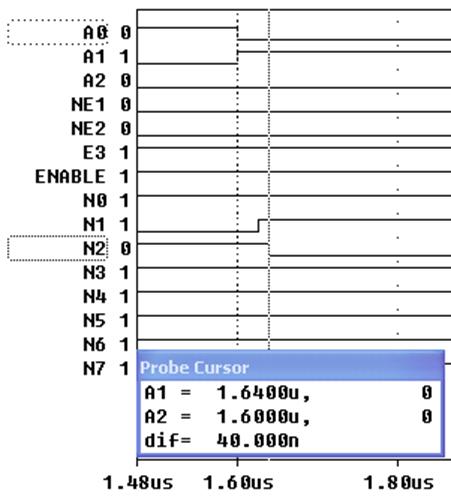

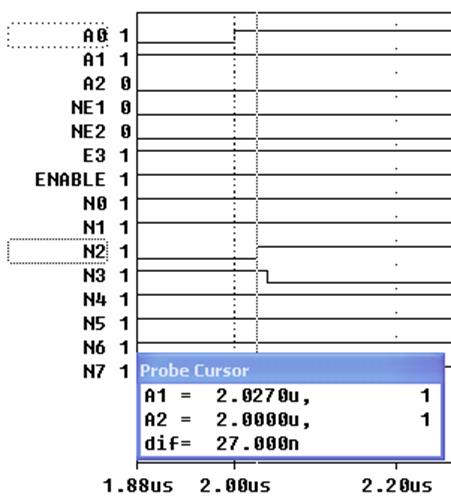

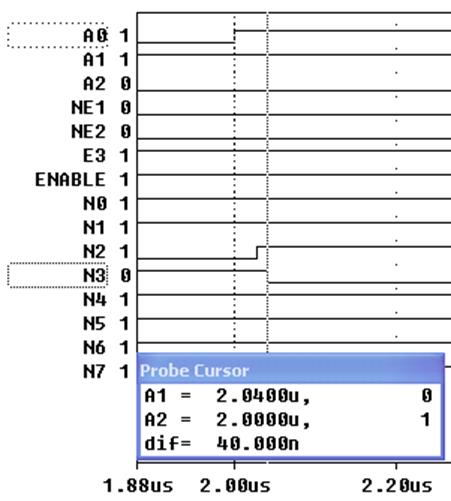

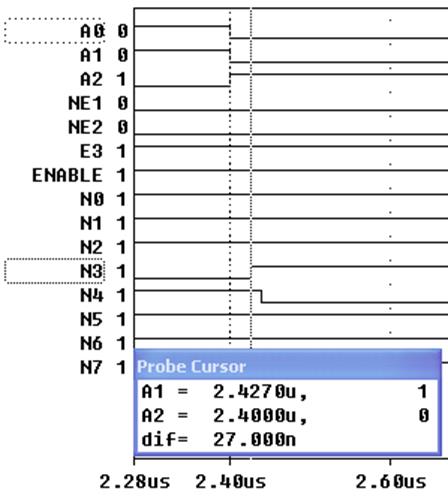

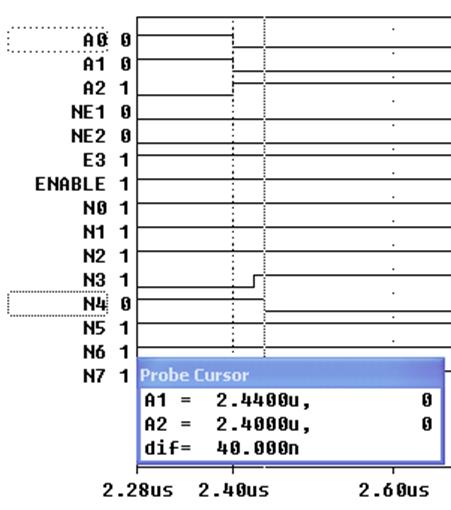

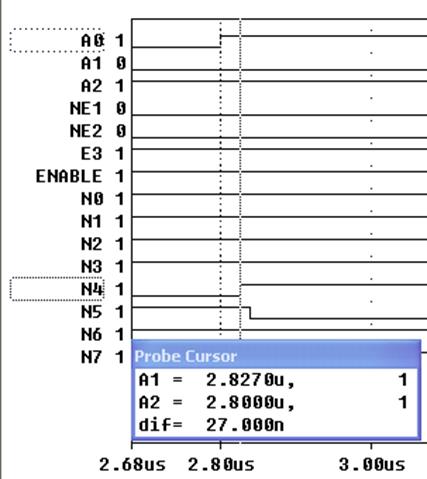

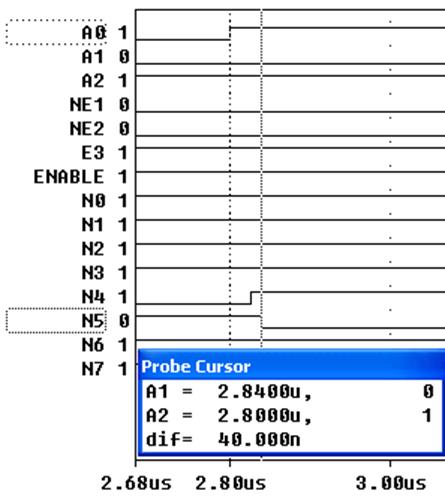

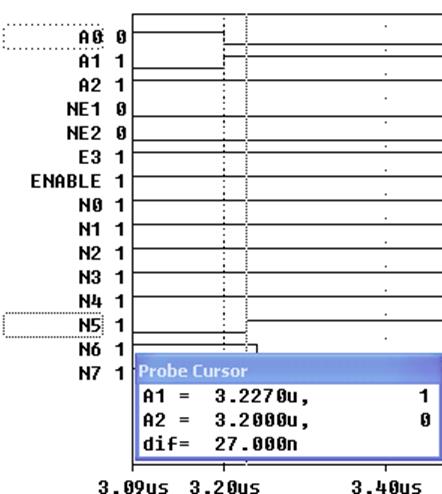

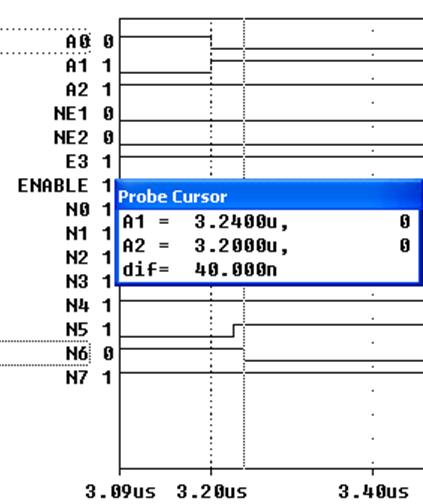

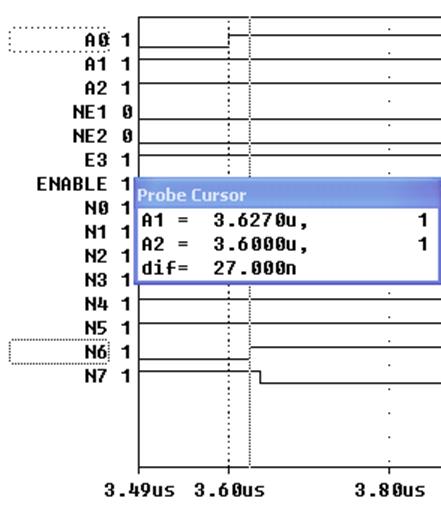

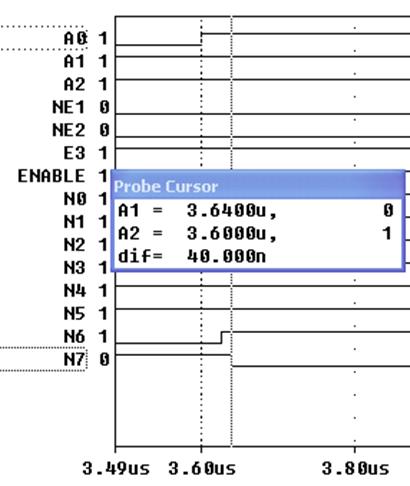

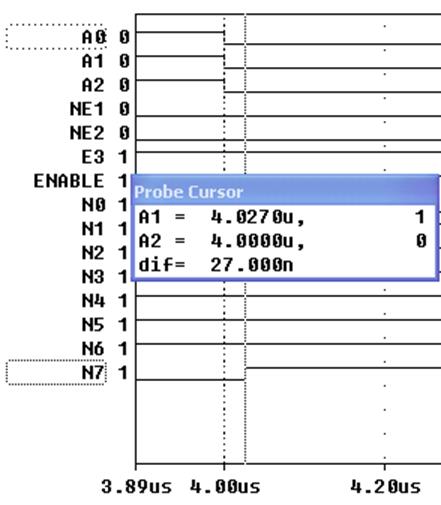

На приведённых ниже временных диаграммах показаны все случаи задержек распространения сигналов.

Рис. 11. Задержка tPLH от

ENABLE для

Рис. 11. Задержка tPLH от

ENABLE для

![]() . Рис.

12. Задержка tPHL от ENABLE для

. Рис.

12. Задержка tPHL от ENABLE для ![]() .

.

Рис. 13. Задержка tPLH от SELECT для

Рис. 13. Задержка tPLH от SELECT для![]() . Рис.

14. Задержка tPHL от SELECT для

. Рис.

14. Задержка tPHL от SELECT для ![]() .

.

Рис. 15. Задержка tPHL от SELECT для ![]() .

Рис. 16. Задержка tPLH от

SELECT для

.

Рис. 16. Задержка tPLH от

SELECT для ![]() .

.

Рис. 17. Задержка tPHL от

SELECT для ![]() . Рис. 18. Задержка tPLH от

SELECT для

. Рис. 18. Задержка tPLH от

SELECT для ![]() .

.

Рис. 19. Задержка tPHL от SELECT для ![]() .Рис. 20. Задержка tPLHот SELECT для

.Рис. 20. Задержка tPLHот SELECT для ![]() .

.

Рис. 21. Задержка tPHL от SELECT для ![]() .Рис. 22. Задержка tPLH от SELECT для

.Рис. 22. Задержка tPLH от SELECT для ![]() .

.

Рис. 23. Задержка tPHL от SELECTдля

![]() .Рис. 24. Задержка tPLH от

SELECT для

.Рис. 24. Задержка tPLH от

SELECT для ![]() .

.

Рис. 25. Задержка tPHL от SELECT для ![]() .

Рис. 26. Задержка tPLH от

SELECT для

.

Рис. 26. Задержка tPLH от

SELECT для ![]() .

.

Рис. 27. Задержка tPHL от A SELECT для ![]() . Рис.

28. Задержка tPLH от SELECTдля

. Рис.

28. Задержка tPLH от SELECTдля

![]() .

.

Все задержки, показанные на временных диаграммах совпадают с табличными, что является подтверждением правильности их имитирования.

7.7. Оценка предельных скоростных возможностей исследуемого узла

Заранее ясно, что частота не может быть выше заложенной в модель задержек. Предельная частота изменения сигналов на входах узла– величина, обратная максимальной задержке распространения сигнала от входа до выхода.

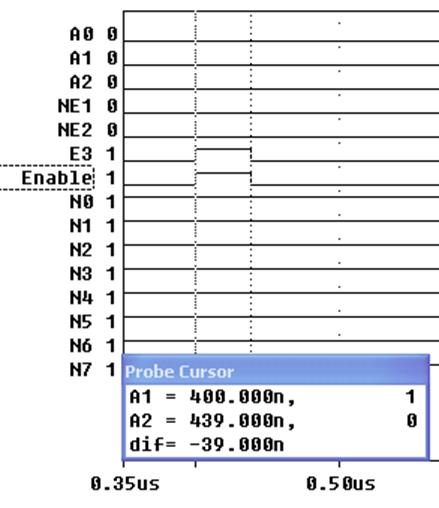

На рис. 29

приведен пример, того, как время удержания сигнала Enable

= 1 мало для того, чтобы схема успела среагировать и дешифратор «включился» на

работу. Данное время не должно быть менее чем время 40ns,

в примере данное время равно 39ns. Следовательно,

частота работы по данному входу на включение дешифратора не должна быть более

чем  Гц = 25 MГц.

Гц = 25 MГц.

Рис.29. Нарушение временных соотношений.

7.8. Функциональное описание проектируемого узла

* K555ID7MDECODER/DEMULTIPLEXER 3-8 LINE

*

* TTL LOGIC STANDARD TTL, S, LS DATA BOOK, APR 1988, TI

* JLS 8-4-92 REMODELED USING LOGICEXP, PINDLY, AND CONSTRAINT DEVICES

*

**Директива начала макромодели

.SUBCKT K555ID7M G1_I G2ABAR_I G2BBAR_I A_I B_I C_I

+ Y0_O Y1_O Y2_O Y3_O Y4_O Y5_O Y6_O Y7_O

+ OPTIONAL: DPWR=$G_DPWR DGND=$G_DGND

+ PARAMS: MNTYMXDLY=0 IO_LEVEL=0

*

**Логический блок. Описывает логику работы элемента

UID7_MLOG LOGICEXP (6,15) DPWR DGND

+ G1_I G2ABAR_I G2BBAR_I A_I B_I C_I **Входы в логический блок

+ G1 G2ABARG2BBARABCENABLE

+ Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 **Выходы из логического блока

+ D0_GATE IO_LS

+ IO_LEVEL={IO_LEVEL}

+

+ LOGIC:**Логическая секция

+ G1 = { G1_I }

+ G2ABAR = { G2ABAR_I }

+ G2BBAR = { G2BBAR_I }

+ A = { A_I }

+ B = { B_I }

+ C = { C_I }

+ ABAR = { ~A }

+ BBAR = { ~B }

+ CBAR = { ~C }

+ ENABLE = { ~G2ABAR & ~G2BBAR & G1 }

+ Y0 = { ~(ENABLE & CBAR & BBAR & ABAR) }

+ Y1 = { ~(ENABLE & CBAR & BBAR & A ) }

+ Y2 = { ~(ENABLE & CBAR & B & ABAR) }

+ Y3 = { ~(ENABLE & CBAR & B & A ) }

+ Y4 = { ~(ENABLE & C & BBAR & ABAR) }

+ Y5 = { ~(ENABLE & C & BBAR & A ) }

+ Y6 = { ~(ENABLE & C & B & ABAR) }

+ Y7 = { ~(ENABLE & C & B & A ) }

*

** Блок задержек. Он отвечает за моделируемые временные задержки

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.