UID7_MDLY PINDLY (8,0,7) DPWR DGND

+ Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 **Вычисляется задержка для данных сигналов

+ ENABLEG1 G2ABARG2BBARABC** Сигналы, от которых зависит задержка

+ Y0_OY1_OY2_OY3_OY4_OY5_OY6_OY7_O**Выходы из данного блока

+ IO_LS

+ MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

+

+ BOOLEAN: **Переменные переключения сигнала

+ ABLE1 = { CHANGED(ENABLE,0) }

+ ADDRA = { CHANGED(A,0) }

+ ADDRB = { CHANGED(B,0) }

+ ADDRC = { CHANGED(C,0) }

+ ADDR = { CHANGED(A,0) | CHANGED(B,0) | CHANGED(C,0) }

+

+ PINDLY: **В этом блоке моделируются задержки

+ Y0_OY1_OY2_OY3_OY4_OY5_OY6_OY7_O = {

+ CASE (

+ ADDR & TRN_LH, DELAY(-1,-1,27NS), **Задержка (TPLH) от выводов А0,А1,А2

+ ADDR & TRN_HL, DELAY(-1,-1,40NS), **Задержка (TPHL) от выводов А0,А1,А2

+ ABLE1 & TRN_LH, DELAY(-1,-1,27NS), **Задержка (TPLH) от Enable

+ ABLE1 & TRN_HL, DELAY(-1,-1,40NS), **Задержка (TPHL) от Enable

+ DELAY(-1,-1,40NS)

+ )

+ }

*

.ENDS

7.9. Схема верификации символа с подключённой к нему макромоделью

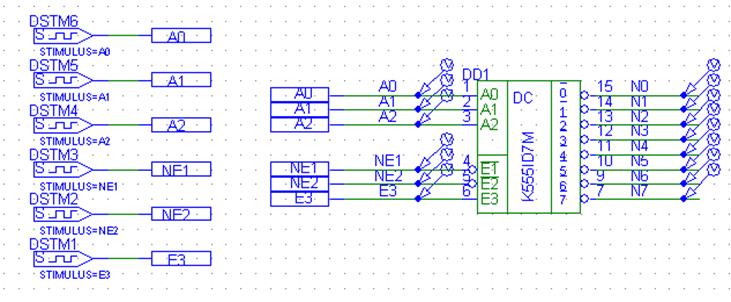

Схема верификации символа с подключённой к нему макромоделью представлена на рис. 30.

Рис. 30. Схема верификации символа с подключённой к нему макромоделью.

7.10. Результаты верификации символа с подключённой к нему макромоделью

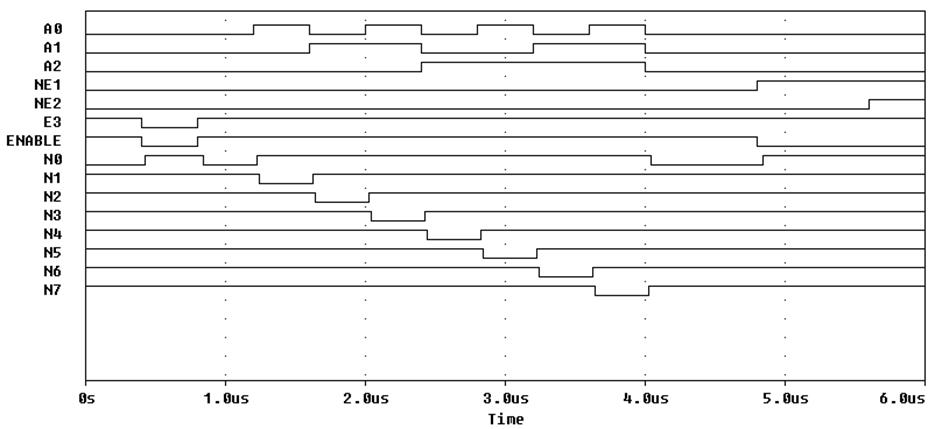

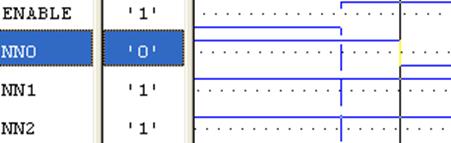

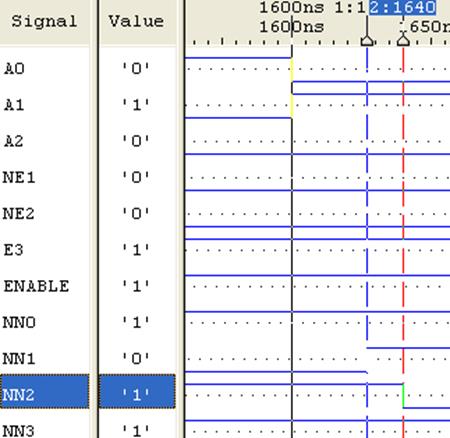

Результаты верификации символа с подключённой к нему макромоделью представлены на рис. 31.

Рис. 31. Результаты верификации символа с подключённой к нему макромоделью.

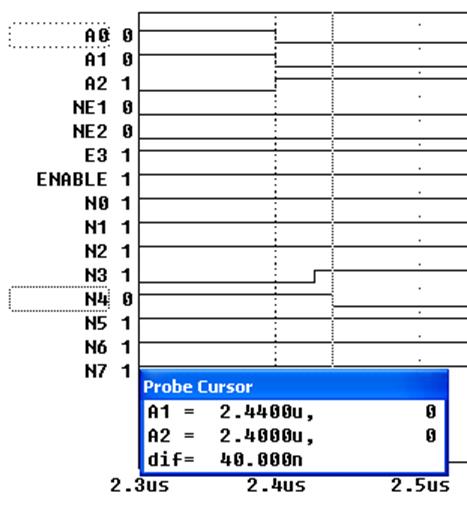

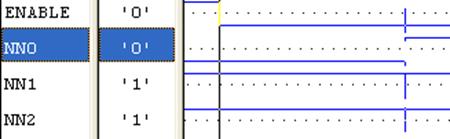

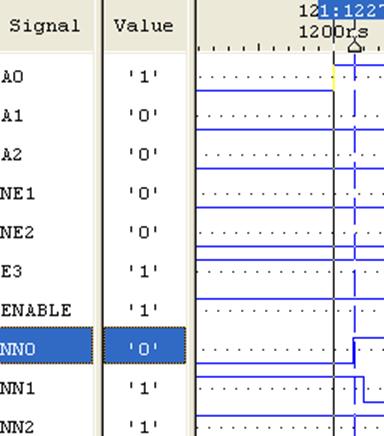

Сигналы внешних воздействий идентичны сигналов из пункта 7.4. Приведенная диаграмма идентична временной диаграмме приведенной на рис.10. Исходя из выше сказанного, приводится один пример задержек (рис.32).

Рис. 32 Задержка

tPHL от SELECT для ![]() .

.

Дальнейшее рассмотрение задержек не имеет смысла, так как они идентичны.

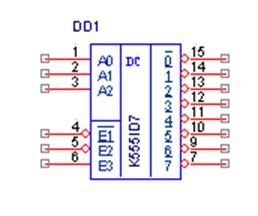

8.1. Иерархический символ проектируемого узла

Иерархический символ проектируемого узла представлен на рис. 33.

.

.

Рис. 33. Иерархический символ проектируемого узла.

8.2. Схема замещения проектируемого узла

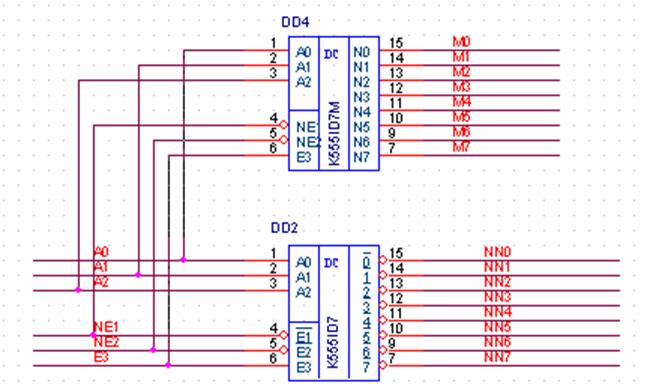

Схема замещения проектируемого узла представлена на рис. 34.

Рис. 34. Схема замещения проектируемого узла.

VHDL-модели всех элементов данной схемы представлены в приложении 2.

8.3. Схема верификации иерархического символа

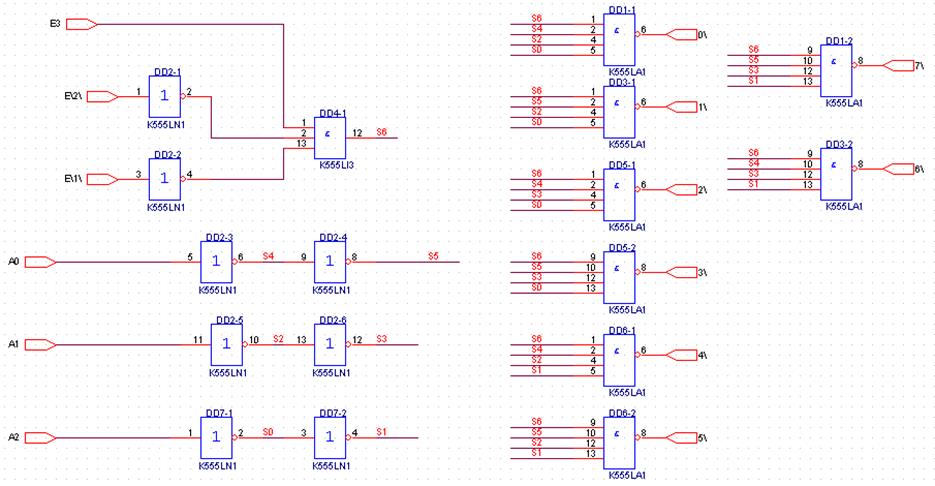

Схема верификации иерархического символа со схемой замещения и с VHDL -моделью представлена на рис.35.

Рис. 35. Схема верификации иерархических символов.

8.4. Результаты моделирования узла

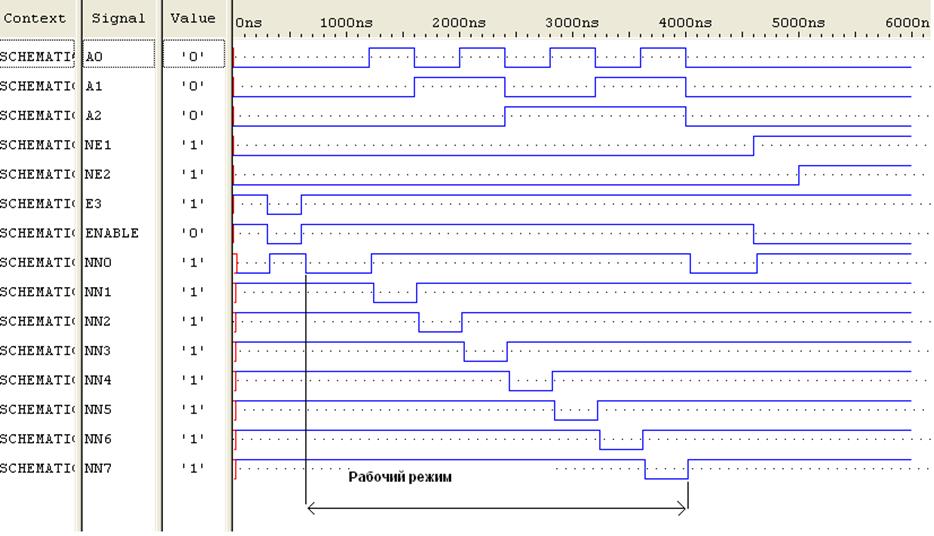

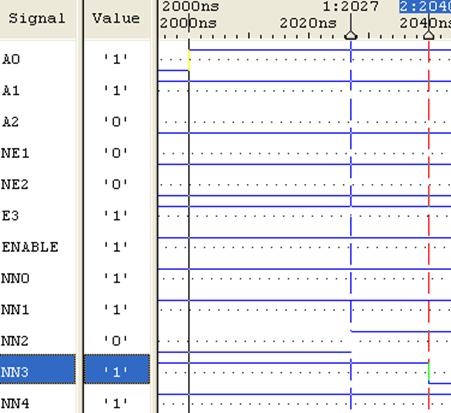

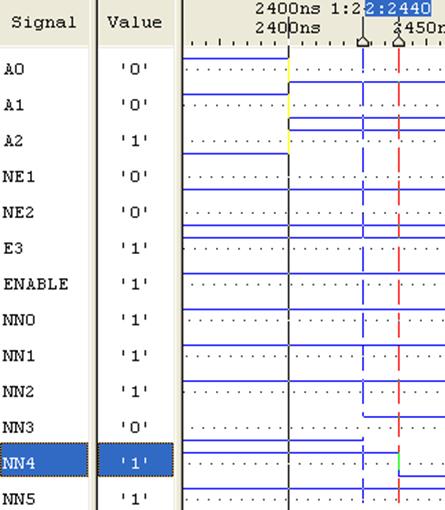

Результаты моделирования узла в виде временных диаграмм представлены на рис. 36.

Рис. 36. Результаты моделирования узла

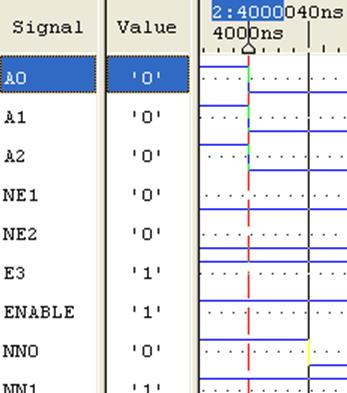

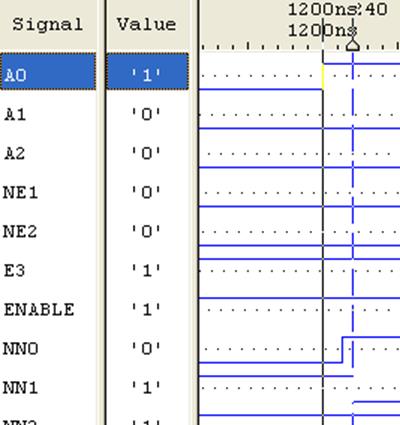

На приведённых ниже временных диаграммах показаны все случаи задержек распространения сигналов.

![]()

![]()

Рис. 37. Задержка tPLH от

ENABLE для ![]() (27ns). Рис. 38. Задержка tPHL

от ENABLE для

(27ns). Рис. 38. Задержка tPHL

от ENABLE для![]() (40ns).

(40ns).

![]()

![]()

Рис. 39. Задержка tPLH отSELECT для![]() (27ns). Рис. 40. Задержка tPHL

отSELECTдля

(27ns). Рис. 40. Задержка tPHL

отSELECTдля![]() (40ns).

(40ns).

![]()

![]()

Рис. 41. Задержка tPHL от SELECT для ![]() (40ns) .

Рис. 42. Задержка tPLH от

SELECT для

(40ns) .

Рис. 42. Задержка tPLH от

SELECT для ![]()

(27ns) и tPHL от

SELECT для ![]() (40ns).

(40ns).

![]()

![]()

Рис. 43. Задержка tPHL от

SELECT для ![]() (40ns) Рис.

44. Задержка tPLH от

SELECT для

(40ns) Рис.

44. Задержка tPLH от

SELECT для ![]()

и tPLH от

SELECT для ![]() (27ns) .

(27 ns) и tPHL от

SELECT для

(27ns) .

(27 ns) и tPHL от

SELECT для ![]() (40 ns).

(40 ns).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.