|

Обозначение |

Время распространения сигнала: |

Максимальное значение, нс |

|

tPLH |

Время (задержка) распространения сигнала при переходе из активного состояния в пассивное[1]: - от выводов A0,A1,A2 (SELECT) к выводам - от вывода ENABLE

= E3 and not( |

27 27 |

|

tPHL |

Время задержки распространения сигнала при переходе из пассивного состояния в активное: - от выводов A0,A1,A2 (SELECT) к выводам - от вывода ENABLE

= E3 and not( |

40 40 |

Микросхема К555ИД7

представляет собой дешифратор 3 в 8. Зарубежный аналог DM74LS138.

Для того чтобы дешифратор начал выбирать

по поступившим адресам линии необходимо, чтобы ENABLE = E3 and not(![]() ) and not(

) and not(![]() ) принял единичный

уровень (это реализуется при E3 = 1,

) принял единичный

уровень (это реализуется при E3 = 1, ![]() =0,

=0, ![]() =0), т.е. фактически, разрешить работу.

После данного действия дешифратор выбирает линию по поступившим адресам (А0,А1,А2)

и переводит её в активное состояние. Для прекращения работы дешифратора, т.е.

перевода всех выходов в пассивное состояние, необходимо подать сигнал нулевого

уровня на вход разрешения.

=0), т.е. фактически, разрешить работу.

После данного действия дешифратор выбирает линию по поступившим адресам (А0,А1,А2)

и переводит её в активное состояние. Для прекращения работы дешифратора, т.е.

перевода всех выходов в пассивное состояние, необходимо подать сигнал нулевого

уровня на вход разрешения.

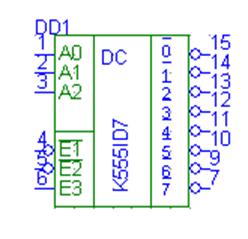

7.1. Условное графическое изображение проектируемого узла в виде иерархического символа

Условное графическое изображение проектируемого узла в виде иерархического символа представлено на рис. 2.

Рис. 2. Условное графическое изображение проектируемого узла в виде иерархического символа.

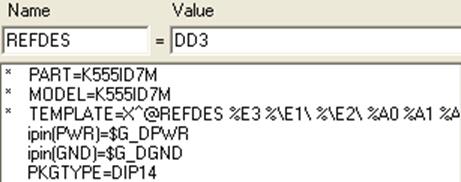

Естественно, что УГО для узла с макромоделью выполнено таким же образом, что и рассматриваемое УГО. На рис.3 приведены атрибуты символа (с макромоделью), для контроля со стороны преподавателя правильности действий.

TEMPLATE = X^@REFDES %E3 %\E1\ %\E2\ %A0 %A1 %A2 %N0 %N1 %N2 %N3 %N4 %N5 %N6 %N7 %PWR %GND @MODEL

Рис.3. Атрибуты символа.

7.2. Схема замещения проектируемого узла

Схема замещения проектируемого узла представлена на рис. 4.

Таблица 4. Список используемых в схеме замещения элементов.

|

74ls04 |

К555LN1 |

Инвертор; количество в упаковке - 6 |

|

74ls11 |

К555LI3 |

Элемент И на 3 входа; количество в упаковке - 3 |

|

74ls20 |

K555LA1 |

Элемент И-НЕ на 4 входа; количество в упаковке - 2 |

Макромодели всех элементов данной схемы представлены в приложении 1.

При создании элементов схемы замещения использовались зарубежные элементы, скопированные из системной библиотеки 74LS.slb, УГО которых преобразованы в соответствии с принятым ГОСТом.

Задержки использованных элементов отличаются от реальных задержек в существующих ИМС. Так же из библиотеки функционального описания элементов – 74LS.LIB были скопированы функциональные описания используемых элементов.

Нулевые задержки на элементах К555LN1 и К555LI3 объясняются тем, что в процессе разработки не удалось подобрать такие задержки элементов, чтобы суммарные задержки были равны табличным.

Рис. 4. Схема замещения проектируемого узла.

7.3. Текстовое SPICE-описание моделируемого узла

Далее приводятся содержания файлов, в которых хранится информация о схеме (*.cir) и файла содержащего список элементов и цепей, содержащихся в данной схеме (*.net).

* C:\MSim_8\Projects\DesignLAB8\Verif2.sch -файл схемы

* Schematics Version 8.0 - July 1997

* Wed Nov 14 15:49:21 2007

** Analysis setup **

.tran 20ns 6000ns -величина шага, время моделирования

* From [SCHEMATICS NETLIST] section of msim.ini:

.lib "C:\MSim_8\Projects\DesignLAB8\Models.lib" -библиотека макромоделей

.lib "nom.lib"

.stmlib "C:\MSim_8\Projects\DesignLAB8\Verif.stl" -файл внешних воздействий

.INC "Verif2.net"

.INC "Verif2.als"

.probe

.END

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.