else W<='1' after 21ns;

end if;

end if;

end if;

else

if B='1' THEN

if C='1' THEN

if D3='1'then W<='0' after 20ns;

else W<='1' after 21ns;

end if;

else

if D2='1'then W<='0' after 20ns;

else W<='1' after 21ns;

end if;

end if;

else

if C='1' THEN

if D1='1'then W<='0' after 20ns;

else W<='1' after 21ns;

end if;

else

if D0='1'then W<='0' after 20ns;

else W<='1' after 21ns;

end if;

end if;

end if;

end if;

end if;

end process;

END model;

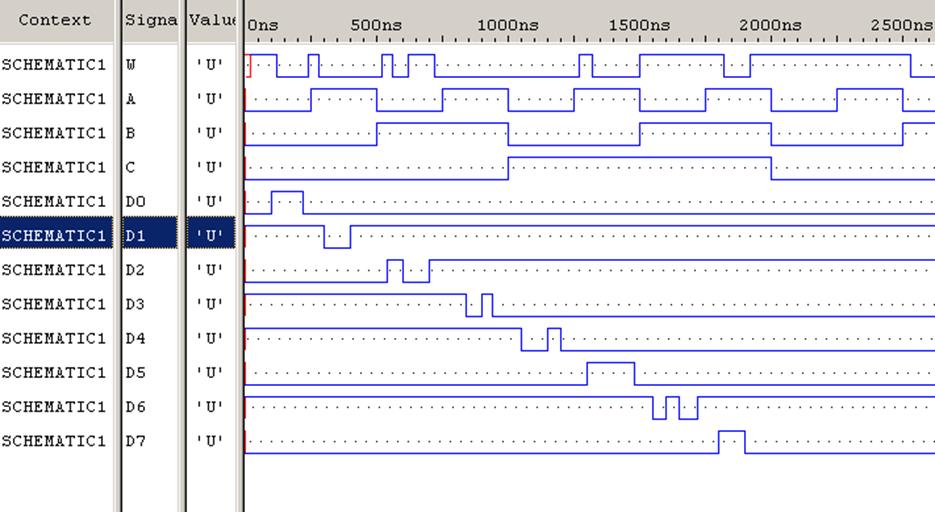

Рис.19. Работа узла с подключённой к нему VHDL-моделью.

Схема верификации узла с подключённой к нему VHDL-моделью, выгледит аналогично схеме верификации узла со схемой замещения.

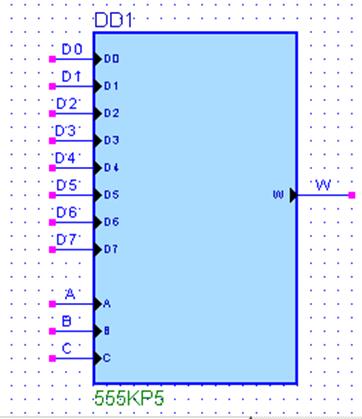

Рис.20. УГО моделируемого узла.

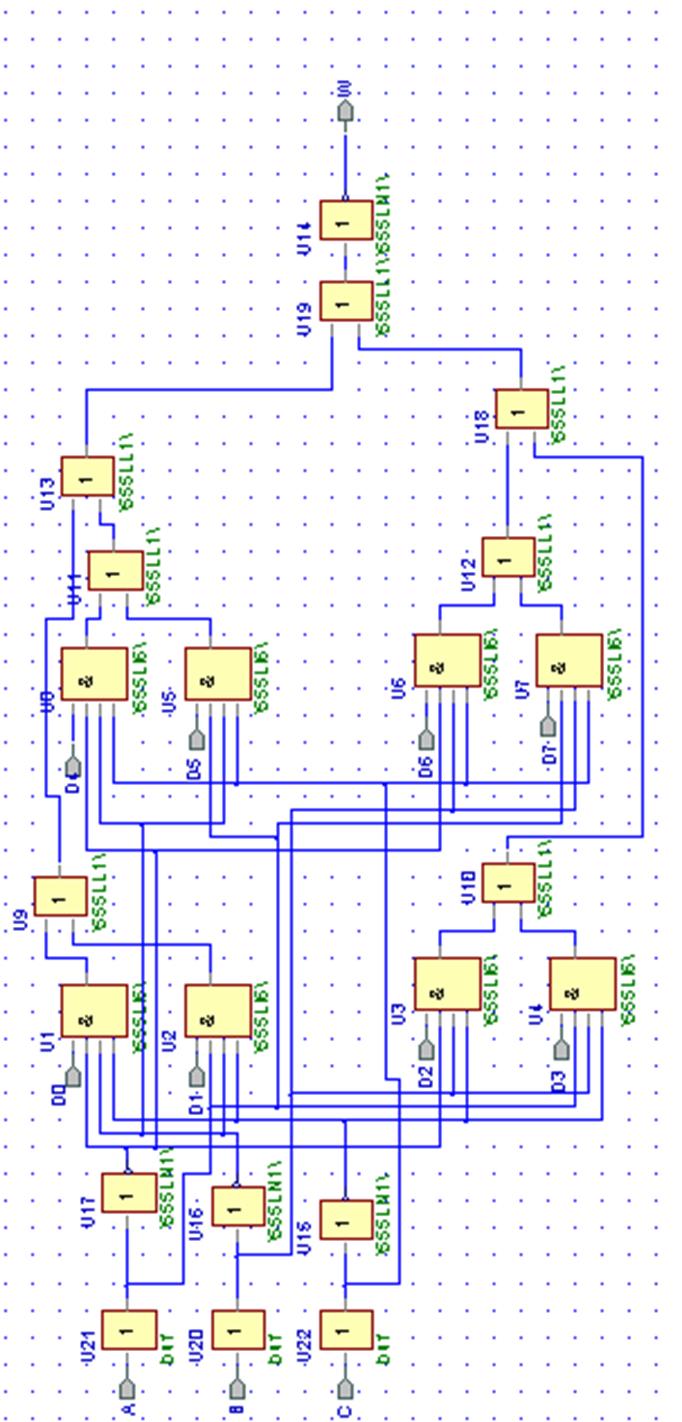

Рис .21.Принципиальная схема замещения проектируемого узла.

Поведенческую модель нашего узла нет необходимости создавать заново, она уже была создана мною ранее при работе с пакетом OrCad и она расположена в пункте 8.5.

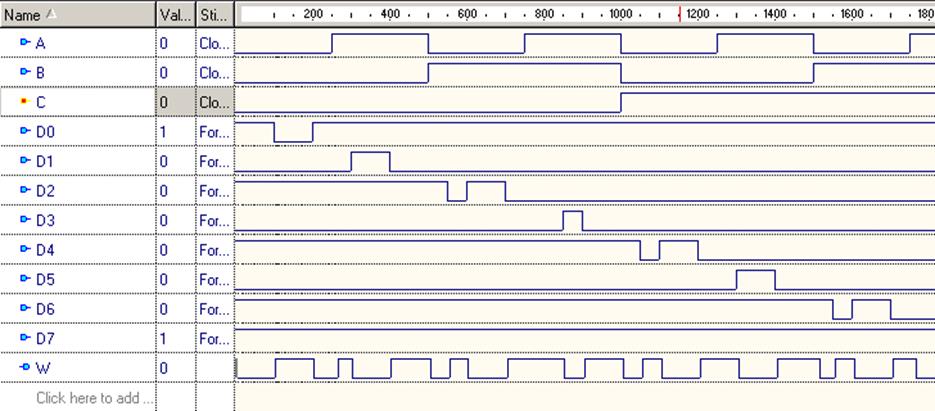

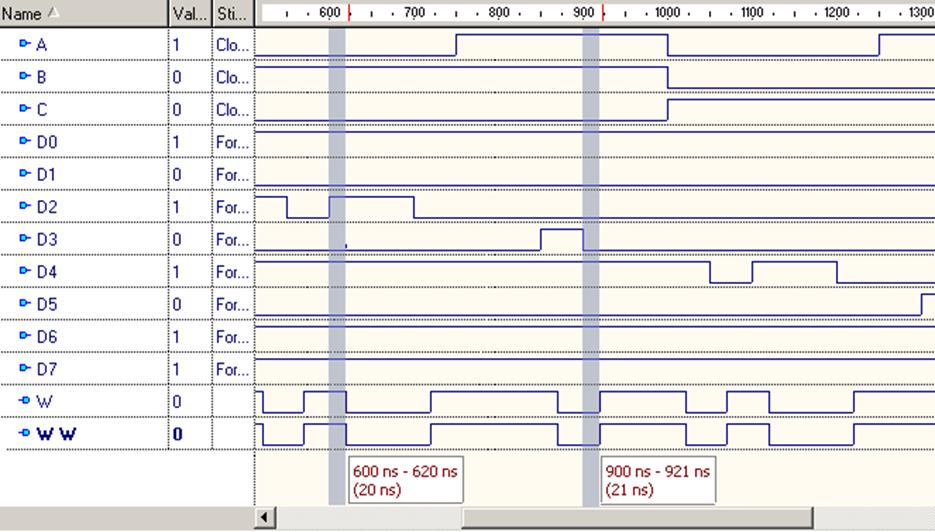

Рис.22.Диаграмма работы узла 555КП5

Рис.23. Задержки распространения от информационных входов до выхода.

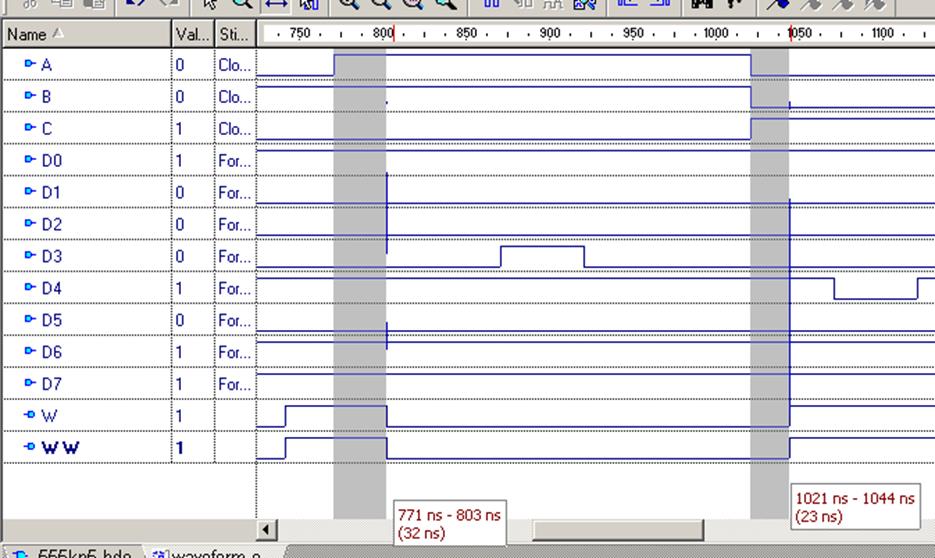

Рис.24. Задержки распространения от информационных входов до выхода.

10. Выводы:

В данной курсовой работе я моделировал мультиплексор 555КП5 в трёх пакетах: DesignLab, Orcad и Active HDL. С двумя из них я уже работал ранее, работу с третьим пришлось освоить самостоятельно.

Поиск литературы по моей микросхеме занял довольно длительный период. Как это не странно, но я ожидал встретить больше документаций по мультиплексорам, но увы. Подготовив библиографический материал, я приступил к разработке узла. Сам процесс начался с тяжёлого этапа воспоминаний позабытых за лета знаний.

Вначале я создал свою библиотеку символов, и скопировал в неё описание и упаковочную информацию для всех элементов своего мультиплексора, изменив при этом графику элементов в соответствии с ГОСТ 2.743-91. Наконец элементная база подготовлена, и я приступил к созданию принципиальной схемы, что может быть приятней, но на этом этапе меня ждали ряд подводных камней, а именно, я перепутал входы. Как следствие схема работала неправильно, пришлось исправлять ошибку. Самым противным этапом было выставления правильных задержек, пришлось добавить 3 буфера на адресных входах, но и эту трудность я преодолел. Осталось подать входные воздействия и оценить работу узла на диаграмме. Работает прекрасно.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.