X_HS1_DD19 D2 $N_0007 $N_0008 $N_0011 $N_0003 $G_DPWR $G_DGND 555LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD14 D4 $N_0007 $N_0009 $N_0010 $N_0012 $G_DPWR $G_DGND 555LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD15 D5 $N_0006 $N_0009 $N_0010 $N_0013 $G_DPWR $G_DGND 555LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD16 D6 $N_0007 $N_0008 $N_0010 $N_0014 $G_DPWR $G_DGND 555LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD17 D7 $N_0006 $N_0008 $N_0010 $N_0015 $G_DPWR $G_DGND 555LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD35 $N_0016 out1 $G_DPWR $G_DGND 555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD34 $N_0017 $N_0018 $N_0016 $G_DPWR $G_DGND 555LL1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD33 $N_0005 $N_0019 $N_0018 $G_DPWR $G_DGND 555LL1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD30 $N_0012 $N_0013 $N_0020 $G_DPWR $G_DGND 555LL1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD31 $N_0014 $N_0015 $N_0019 $G_DPWR $G_DGND 555LL1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD21 D0 $N_0007 $N_0009 $N_0011 $N_0021 $G_DPWR $G_DGND 555LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_U28 $N_0021 $N_0022 $N_0023 $G_DPWR $G_DGND 555LL1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD32 $N_0020 $N_0023 $N_0017 $G_DPWR $G_DGND 555LL1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD20 D1 $N_0006 $N_0009 $N_0011 $N_0022 $G_DPWR $G_DGND 555LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD9 C $N_0010 $G_DPWR $G_DGND 555buf PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD8 B $N_0008 $G_DPWR $G_DGND 555buf PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD7 A $N_0006 $G_DPWR $G_DGND 555buf PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U7 A B C D0 D1 D2 D3 D4 D5 D6 D7 OUT2 $G_DPWR $G_DGND 555KP5 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

* C:\MSim_8\UserLib\DesignLab\MY_MUX.stl written on Mon Dec 02 17:21:04 2002

* by Stimulus Editor -- Serial Number: 100617 -- Version 8.0

;!Stimulus Get

;! DO Digital D1 Digital D2 Digital D3 Digital D4 Digital D5 Digital D6 Digital D7 Digital A Digital B Digital C Digital

;!Ok

;!Plot Axis_Settings

;!Xrange 0s 3.003us

;!AutoUniverse

;!XminRes 1ns

;!YminRes 1n

;!Ok

.STIMULUS DO STIM (1, 1)

+ +0s 0

+ 132ns 1

+ 274ns 0

.STIMULUS D1 STIM (1, 1)

+ +0s 0

+ 190ns 1

+ 561ns 0

+ 711ns 1

.STIMULUS D2 STIM (1, 1)

+ +0s 0

+ 1.343us 1

.STIMULUS D3 STIM (1, 1)

+ +0s 0

+ 910ns 1

+ 1.078us 0

.STIMULUS D4 STIM (1, 1)

+ +0s 0

+ 2.252us 1

+ 2.879us 0

.STIMULUS D5 STIM (1, 1)

+ +0s 0

+ 2.394us 1

+ 2.513us 0

.STIMULUS D6 STIM (1, 1)

+ +0s 0

+ 1.678us 1

+ 1.797us 0

.STIMULUS D7 STIM (1, 1)

+ +0s 0

+ 1.594us 1

+ 2.182us 0

.STIMULUS A STIM (1, 1)

+ +0s 0

+ 406ns 1

+ 1.201us 0

+ 1.886us 1

+ 2.659us 0

.STIMULUS B STIM (1, 1)

+ +0s 0

+ 790ns 1

+ 2.305us 0

.STIMULUS C STIM (1, 1)

+ +0s 0

+ 1.537us 1

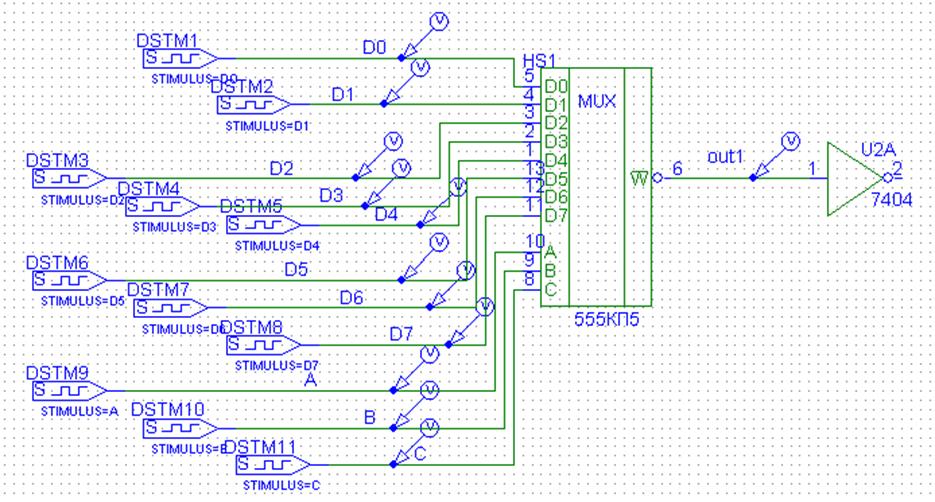

Рис.5. Схема верификации уза 555КП5.

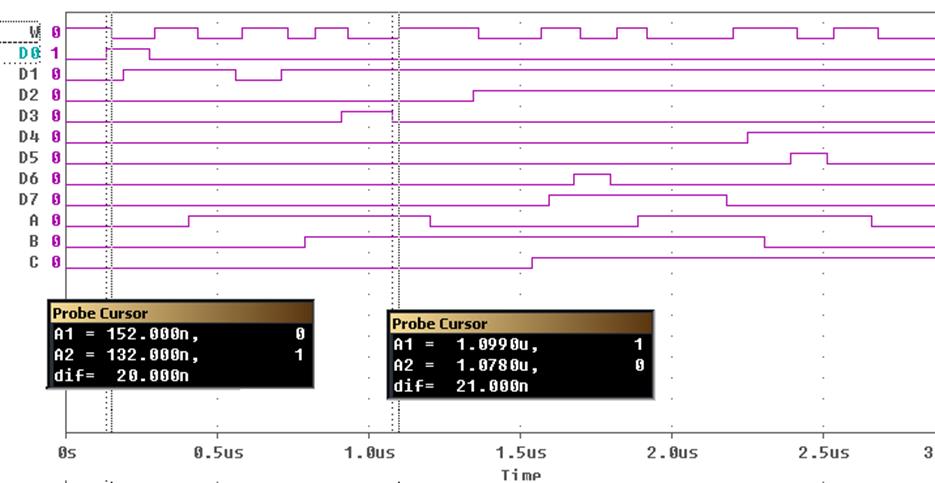

Рис6. Задержки распространения от информационных входов до выхода.

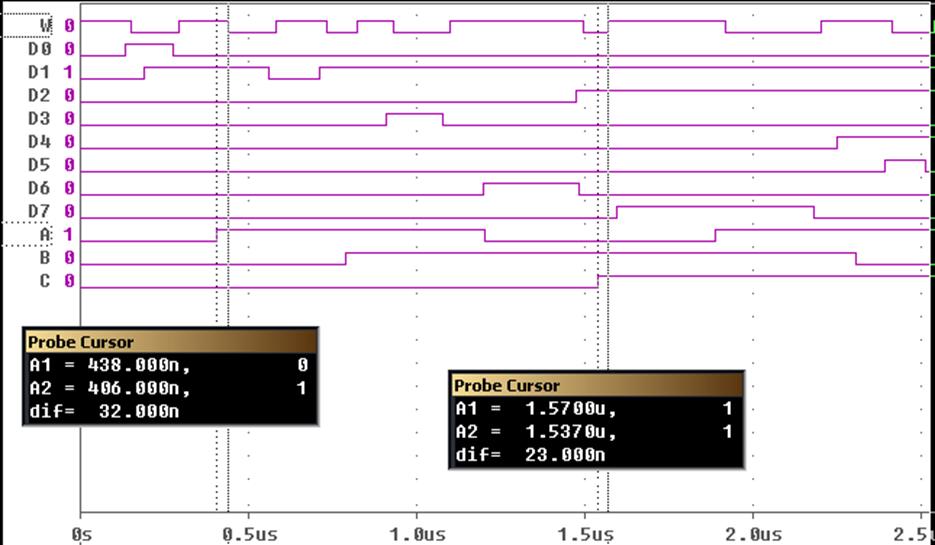

Рис.7.Задержки

распространения от адресных входов до выхода.

Рис.7.Задержки

распространения от адресных входов до выхода.

Как видно на рис.6. и рис.7. смоделированный нами узел работает правельно и временные задержки соблюдены.

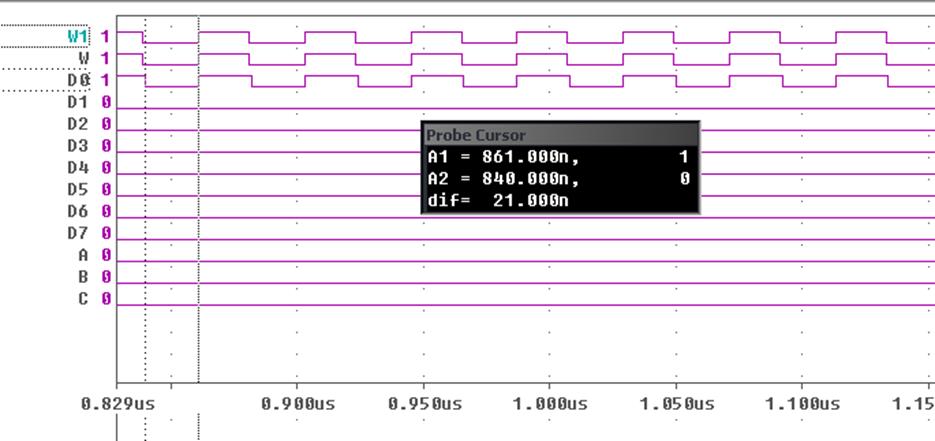

Смоделированный мною узел показал стабильную роботу при частоте изменения сигнала на адресном входе(сигналы на входе данных постоянны) меньшей 15.5 MНz. И при постоянном сигнале на адресных входах, но изменяющемся сигнале на входе данных с частотой меньшей 23.8MHz. Эти результаты можно наблюдать на рис 8. рис.9 и рис.10.

Узел показал нестабильную работу при частоте большей, чем 15.6MHz .W сигнал выхода с модели со схемой замещения,W1 с выхода функционального узла оформленного в виде макромодели.

Рис. 8. Демонстрация скоростных свойств узла при частоте 23.8MHz

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.