Работа стабильная.

.

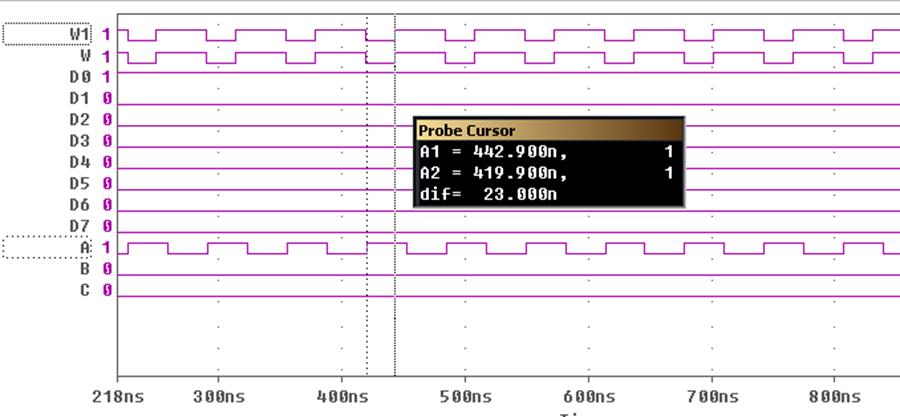

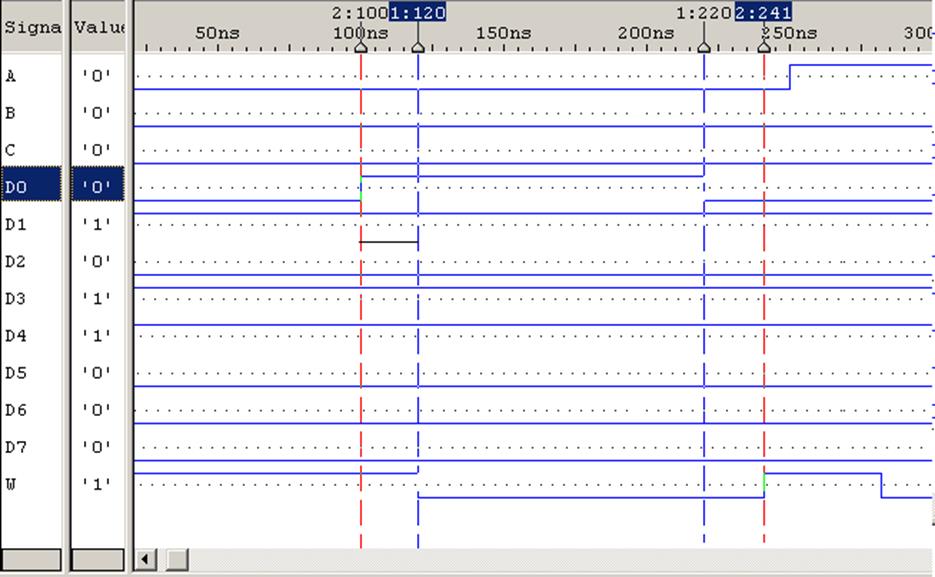

Рис.9. Демонстрация скоростных свойств узла при частоте 15.5MHz

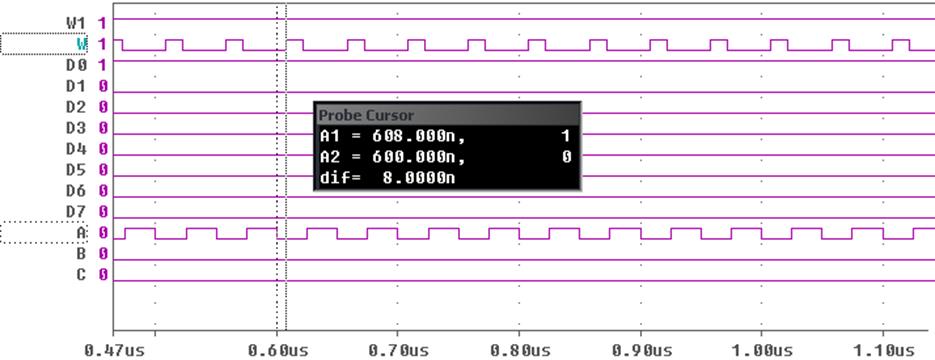

Работа стабильная.

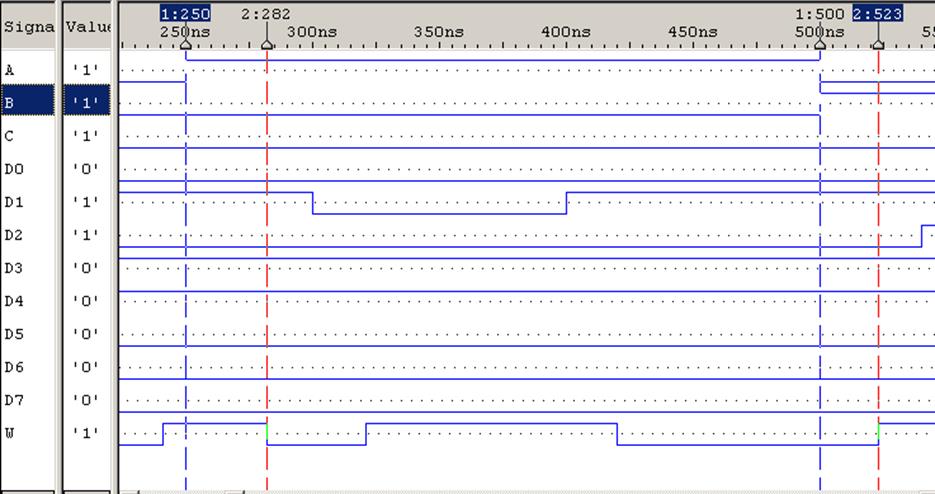

Рис.10. Демонстрация скоростных свойств узла при частоте 16MHz. Узел работает не корректно.

* 555KP5 MULTIPLEXER/DATA SELECTOR 8-1 LINE

*

.SUBCKT 555KP5 A_I B_I C_I D0_I D1_I D2_I D3_I D4_I D5_I D6_I D7_I W_O

+ OPTIONAL: DPWR=$G_DPWR DGND=$G_DGND

+ PARAMS: MNTYMXDLY=0 IO_LEVEL=0

*

ULSKP5LOG LOGICEXP(11,12) DPWR DGND* БЛОКЛОГИКИ

+ A_I B_I C_I D0_I D1_I D2_I D3_I D4_I D5_I D6_I D7_I

+ A B C D0 D1 D2 D3 D4 D5 D6 D7 W

+ D0_GATE IO_LS IO_LEVEL={IO_LEVEL}

+ LOGIC:

+ A = { A_I }

+ B = { B_I }

+ C = { C_I }

+ D0 = { D0_I }

+ D1 = { D1_I }

+ D2 = { D2_I }

+ D3 = { D3_I }

+ D4 = { D4_I }

+ D5 = { D5_I }

+ D6 = { D6_I }

+ D7 = { D7_I }

+ IA = { ~A }

+ IB = { ~B }

+ IC = { ~C }

+ ID0 = { D0 & IA & IB & IC }

+ ID1 = { D1 & A & IB & IC }

+ ID2 = { D2 & IA & B & IC }

+ ID3 = { D3 & A & B & IC }

+ ID4 = { D4 & IA & IB & C }

+ ID5 = { D5 & A & IB & C }

+ ID6 = { D6 & IA & B & C }

+ ID7 = { D7 & A & B & C }

+ W = { ~(ID0 | ID1 | ID2 | ID3 | ID4 | ID5 | ID6 | ID7) }

*

ULSKP5DLY PINDLY (1,0,11) DPWR DGND*БЛОКЗАДЕРЖЕК

+ W

+ A B C D0 D1 D2 D3 D4 D5 D6 D7

+ W_O

+ IO_LS MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

+ BOOLEAN:

+ DATA = { CHANGED(D0,0) | CHANGED(D1,0) | CHANGED(D2,0) | CHANGED(D3,0) |

+ CHANGED(D4,0) | CHANGED(D5,0) | CHANGED(D6,0) | CHANGED(D7,0) }

+ SELECT = { CHANGED(A,0) | CHANGED(B,0) | CHANGED(C,0) }

+ PINDLY:

+ W_O = {

+ CASE(

+ SELECT & TRN_HL, DELAY(-1,32NS,32NS),

+ SELECT & TRN_LH, DELAY(-1,23NS,23NS),

+ DATA & TRN_LH, DELAY(-1,21NS,21NS),

+ DATA & TRN_HL, DELAY(-1,20NS,20NS),

+ DELAY(-1,21NS,33NS)

+ )

+ }

*

.ENDS

*

*$

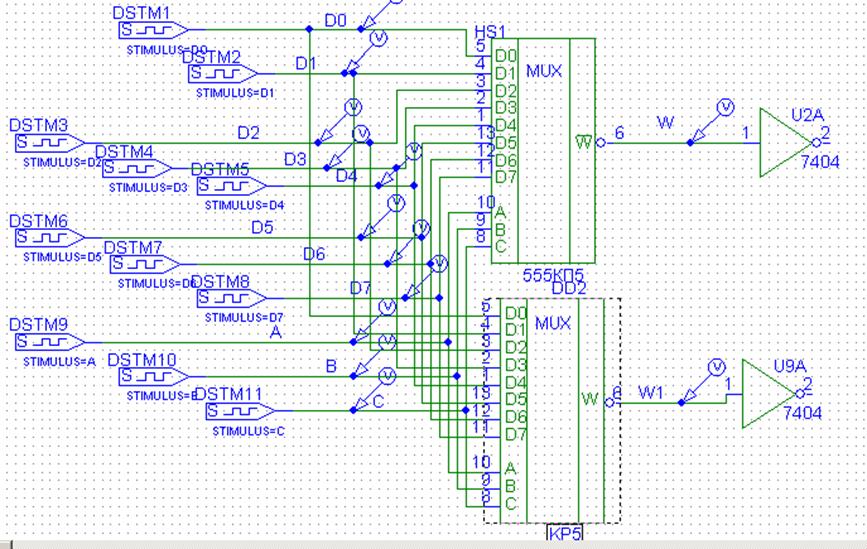

Рис.11. Схема верификации символа с подключённой к нему макромоделью.

Рис. 12. График из постпроцессора моделирования

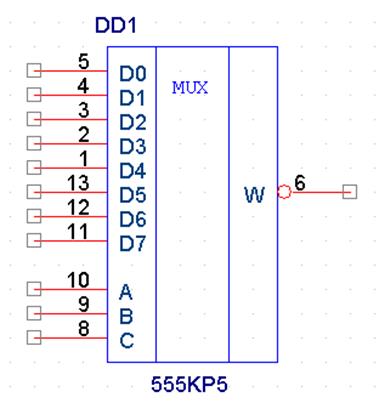

Рис. 13. УГО моделируемого узла

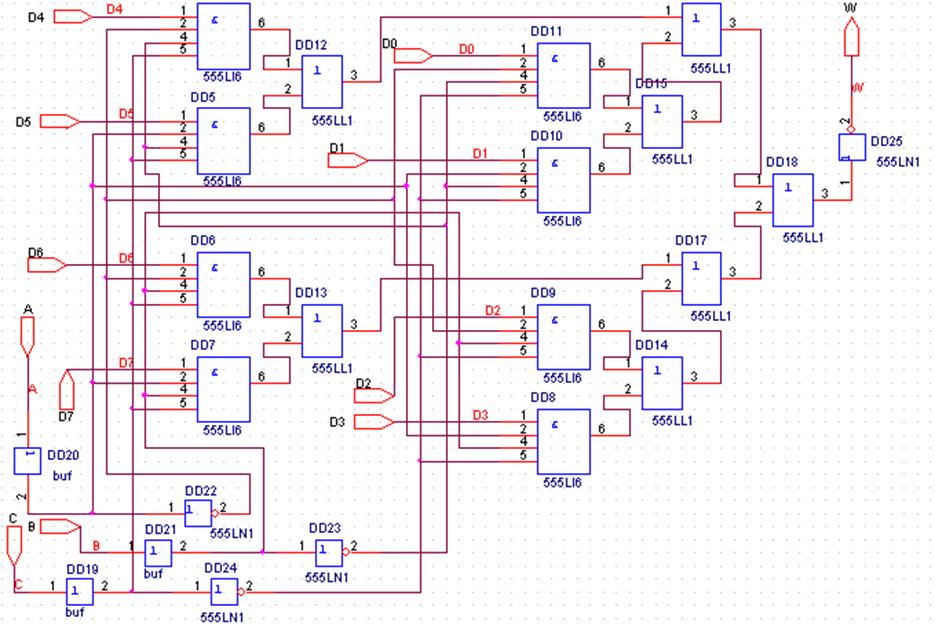

Рис. 14. Принципиальная схема моделируемого узла.

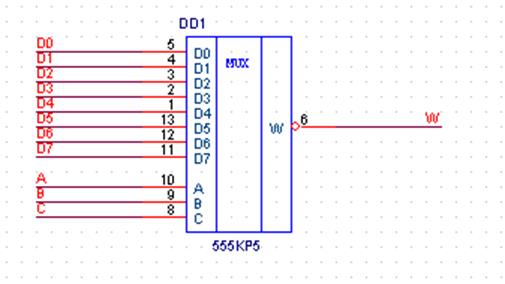

Рис. 15. Схема верификации моделируемого узла

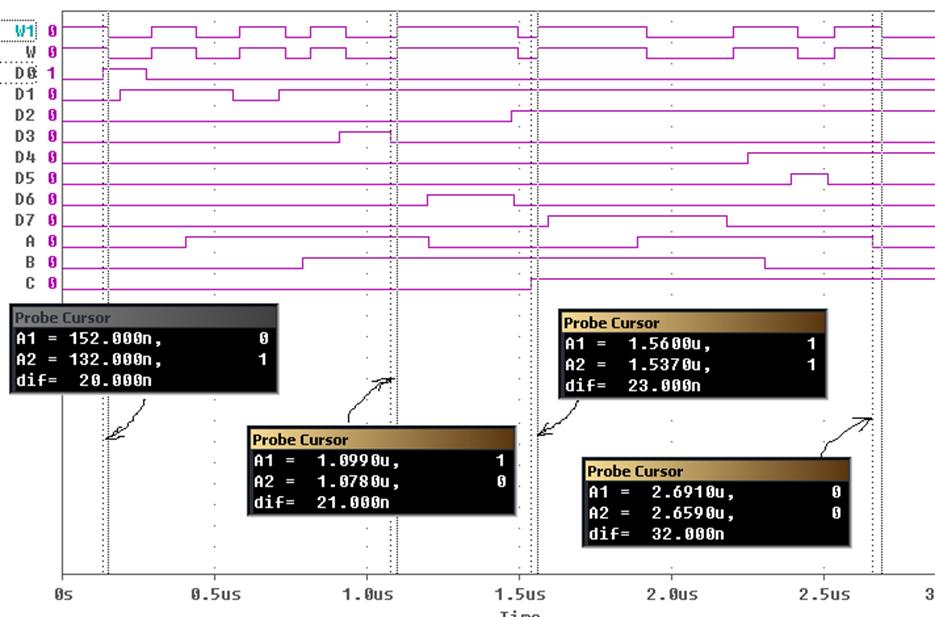

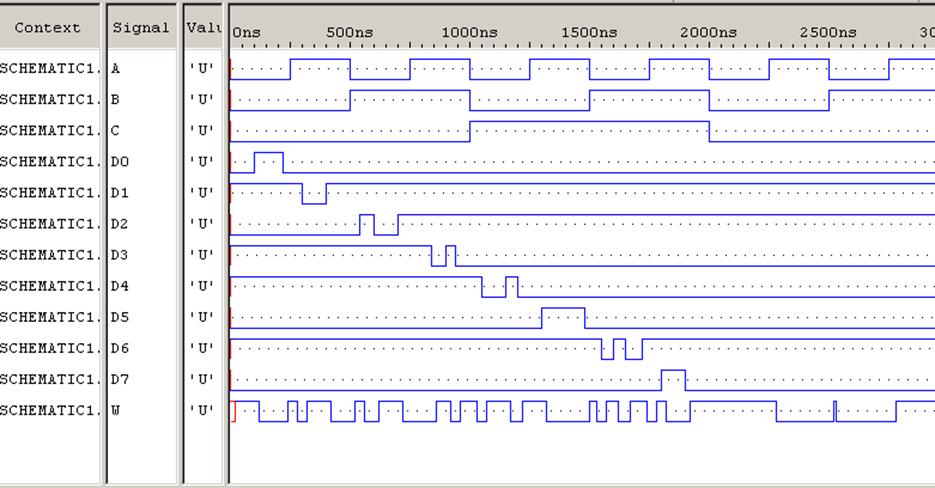

Рис.16.Диаграмма работы узла 555КП5

Рис.17. Задержки распространения от информационных входов до выхода.

Рис.18. Задержки распространения от адресных входов до выхода.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY \555KP5\ IS PORT(

D0 : IN std_logic;

D1 : IN std_logic;

D2 : IN std_logic;

D3 : IN std_logic;

D4 : IN std_logic;

D5 : IN std_logic;

D6 : IN std_logic;

D7 : IN std_logic;

A : IN std_logic;

B : IN std_logic;

C : IN std_logic;

W : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic);

END \555KP5\;

ARCHITECTURE model OF \555KP5\ IS

BEGIN

process(D0,D1,D2,D3,D4,D5,D6,D7,A,B,C)

begin

if (A'EVENT OR B'EVENT OR C'EVENT) THEN //изменение (событие) на селекторных входах

IF A ='1' THEN //определение с какого входа данных

if B='1' THEN поступит информация на выход

if C='1' THEN //задержка при переходе выхода:

if D7='1'then W<='0' after 32ns; //- в состояние «0»

else W<='1' after 23ns; //- в состояние «1»

end if;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.