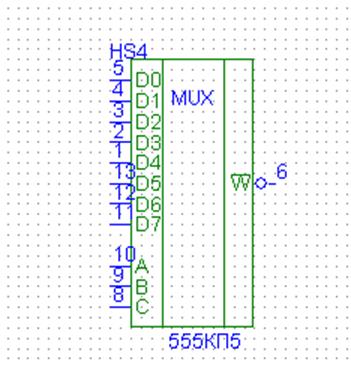

Рис 2. Цоколевка микросхемы 555КП5

4. Логическая таблица режимов работы.

Таблица2. Состояния мультиплексора КП5

|

С |

В |

А |

W |

|

L |

L |

L |

/ D0 |

|

L |

L |

H |

/ D1 |

|

L |

H |

L |

/ D2 |

|

L |

H |

H |

/ D3 |

|

H |

L |

L |

/ D4 |

|

H |

L |

H |

/ D5 |

|

H |

H |

L |

/ D6 |

|

H |

H |

H |

/ D7 |

У моделируемого узла только один режим работы, селекторный.

5. Таблица реальных задержек.

Таблица3. Таблица реальных задержек

|

Задержки распространения (нс) |

|

|

oт D0-D7 до W=LàH |

21 |

|

от D0-D7 до W=HàL |

20 |

|

от A-C до W=LàH |

23 |

|

от A-C до W=HàL |

32 |

Задержки взяты из литературы[3] и соответствуют микросхеме 555 серии.

6. Описание работы моделируемого узла.

Данный

узел представляет собой мультиплексор 8->1 с инверсным выходом, имеет 8

входов данных(D0…D7) и три адресных входа (А,В,С). Работа мультиплексора

описывается формулой: ![]()

Таким образом комбинация на адресных входах определяет с какого входа данных информация поступит на выход, предварительно претерпев операцию инвертирования.

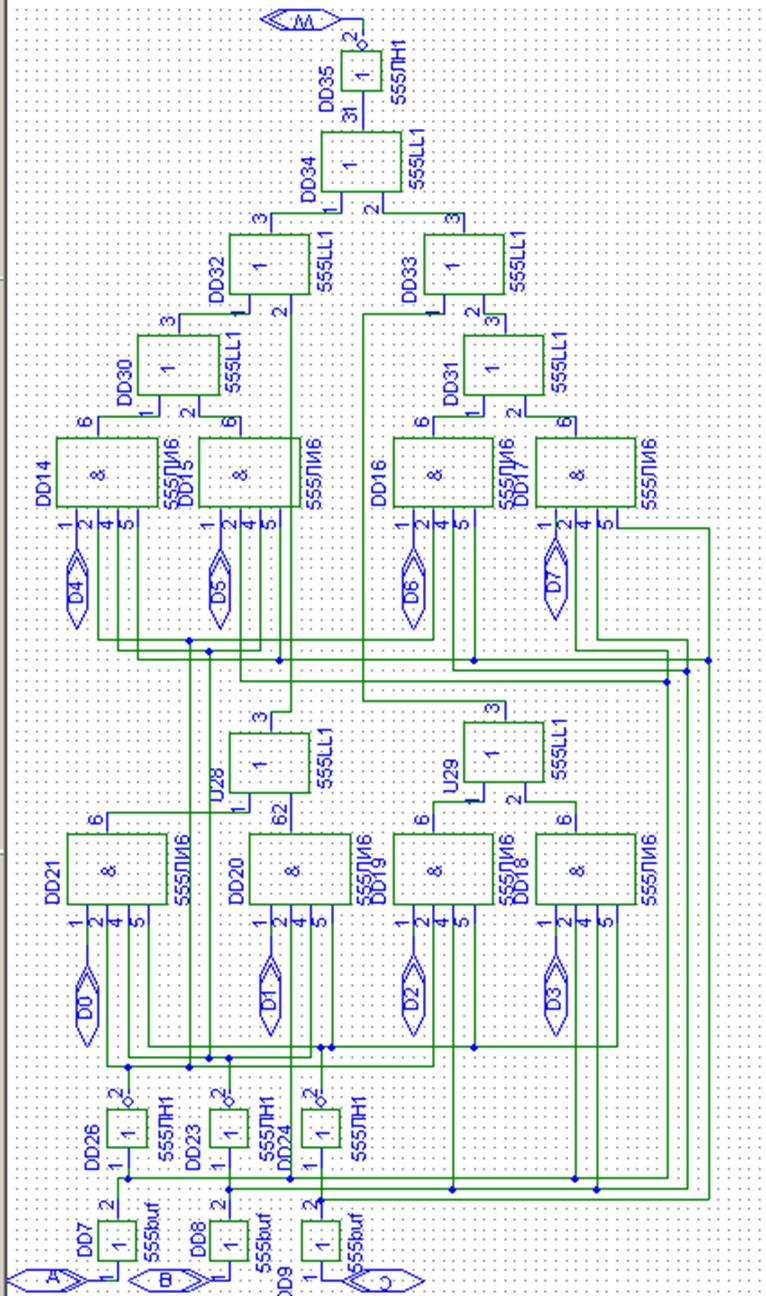

Структурная схема рис. 3. была взята из литературы[2].

Схема состоит из 8 элементов «4 и» и 7 «2 или» и 4 инвертора. На входы каждого из элементов «4и», подаются 3 селекторных сигнала в разных комбинациях (комбинации достигаются с помощью инвертирования селекторных сигналов, т.о. комбинаций 8 на каждый элемент «4и» своя), и сигналы с одного из восьми входов данных. Долее сигналы с выходов этих элементов объединяются с помощью элементов «или» и инвертируются в конце.

рис.3. Структурная схема узла 555КП5.

7. Моделирование узла 555КП5 в оболочке DesignLab 8.0

7.1. Условное графическое изображение моделируемого узла в виде иерархического символа.

Рис4. УГО узла 555КП5

7.2. Схема замещения моделируемого узла.

Рис.5. Принципиальная схема узла 555КП5..

* C:\MSim_8\UserLib\DesignLab\MY_MUX.sch

* Schematics Version 8.0 - July 1997

* Sun Dec 08 14:05:51 2002

** Analysis setup **

.tran 20ns 3000ns

.STMLIB "C:\MSim_8\UserLib\DesignLab\MY_MUX.stl"

* From [SCHEMATICS NETLIST] section of msim.ini:

.lib "C:\MSim_8\UserLib\DesignLab\555.LIB"

.lib "nom.lib"

.INC "MY_MUX.net"

.INC "MY_MUX.als"

.probe

.END

* Schematics Netlist *

X_U2A out1 $N_0001 $G_DPWR $G_DGND 7404 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

U_DSTM11 STIM(1,0) $G_DPWR $G_DGND C IO_STM STIMULUS=C

U_DSTM10 STIM(1,0) $G_DPWR $G_DGND B IO_STM STIMULUS=B

U_DSTM9 STIM(1,0) $G_DPWR $G_DGND A IO_STM STIMULUS=A

U_DSTM8 STIM(1,0) $G_DPWR $G_DGND D7 IO_STM STIMULUS=D7

U_DSTM7 STIM(1,0) $G_DPWR $G_DGND D6 IO_STM STIMULUS=D6

U_DSTM6 STIM(1,0) $G_DPWR $G_DGND D5 IO_STM STIMULUS=D5

U_DSTM5 STIM(1,0) $G_DPWR $G_DGND D4 IO_STM STIMULUS=D4

U_DSTM4 STIM(1,0) $G_DPWR $G_DGND D3 IO_STM STIMULUS=D3

U_DSTM3 STIM(1,0) $G_DPWR $G_DGND D2 IO_STM STIMULUS=D2

U_DSTM2 STIM(1,0) $G_DPWR $G_DGND D1 IO_STM STIMULUS=D1

U_DSTM1 STIM(1,0) $G_DPWR $G_DGND D0 IO_STM STIMULUS=DO

X_U8A OUT2 $N_0002 $G_DPWR $G_DGND 7404 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_U29 $N_0003 $N_0004 $N_0005 $G_DPWR $G_DGND 555LL1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD26 $N_0006 $N_0007 $G_DPWR $G_DGND 555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD23 $N_0008 $N_0009 $G_DPWR $G_DGND 555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD24 $N_0010 $N_0011 $G_DPWR $G_DGND 555LN1 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_HS1_DD18 D3 $N_0006 $N_0008 $N_0011 $N_0004 $G_DPWR $G_DGND 555LI6

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.