|

D7¸D0 |

I/O |

шина данных |

|

INT |

I |

запрос прерывания |

|

HOLD |

I |

захват шины |

|

READY |

I |

готовность |

|

F1 |

I |

тактовый сигнал |

|

F2 |

I |

тактовый сигнал |

|

RESET |

I |

сброс |

|

A15¸A0 |

O |

шина адреса |

|

/WR |

O |

вывод на шину данных |

|

DBIN |

O |

ввод с шины данных |

|

INTE |

O |

разрешение прерывания |

|

HLDA |

O |

подтверждение захвата шины |

|

WAIT |

O |

ожидание |

|

SYNC |

O |

сигнал синхронизации |

Микросхема КР580ИК80 - однокристальный параллельный 8-и разрядный микропроцессор с фиксированной системой команд, имеет раздельные 16-ти разрядный канал адреса и 8-и разрядный канал данных. Канал адреса обеспечивает прямую адресацию внешней памяти объемом 65536 байт, 256 устройств ввода и 256 устройств вывода. Восьмиразрядное АЛУ обеспечивает выполнение арифметических и логических операций над двоичными данными, представленными в доп. коде, а также обработку двоично-десятичных упакованных чисел.

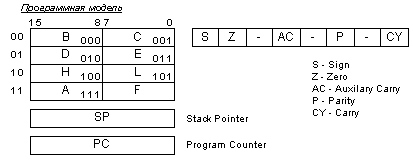

В состав блока регистров входят: 16-ти разрядный регистр адреса команд PC, 16-ти разрядный регистр указателя стека SP, 16-ти разрядный регистр временного хранения WZ (?), шесть 8-и разрядных регистров общего назначения B, C, D, E, H, L, которые могут использоваться как три 16-ти разрядных регистра BC, DE, HL.

|

Существует 4 режима работы ЦП:

· автоматическое исполнение команд (при READY=1)

· ожидание (при READY=0)

· режим ПДП (при HOLD=1)

· режим останова (при выполнении команды HLT)

Режим ожидания может быть использован для согласования работы ЦП с медленнодействующими устройствами, если длительность их цикла обращения составляет более одного периода тактовой частоты, а также для организации пошагового выполнения команд.

При переходе в состояние ПДП ЦП формирует сигнал высокого уровня на выходе HLDA. Буферные схемы канала адреса и данных ЦП переключаются в высокоомное состояние, а выходные управляющие сигналы в состояние низкого уровня, за исключением HLDA и /WR.

В режиме останова ЦП переводит буферные схемы канала адреса и данных в высокоомное состояние. Из данного режима ЦП выходит при наличии сигнала высокого уровня на RESET, HOLD или INT.

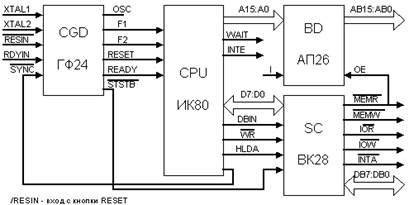

29. Функциональная схема ядра микропроцессорной системы на основе КР580ИК80 и организация системной магистрали

Микропроцессорная система имеет системную шину, образуемую из трех шин: адреса AB15¸AB0, данных DB7¸DB0 и управления. Системная шина позволяет строить микропроцессорную систему по модульному принципу: модуль центрального процессора, модуль ЗУ, модуль УВВ и т.д. Каждый модуль может содержать собственные буферные схемы адреса и данных. Магистральная структура МПС позволяет подключать микросхемы ЗУ общей емкостью до 64КБ и микросхемы УВВ до 256 каналов ввода и 256 каналов вывода.

|

XTAL1,XTAL2 - подключение внешнего сигнала

/RESIN - вход с кнопки RESET

Состав машинного цикла:

Т1 - на шину адреса выдается адреc памяти или устройства ввода/вывода, на шину данных выдаются управляющие сигналы, которые защелкиваются в SC. Для защелкивания процеcсор выдает сигнал SYNC.

Т2 - анализируются сигналы READY, HOLD

T3 - обмен данными с ОЗУ, стеком и УВВ

Т4,Т5 - выполнение операции

43. Структура и основные характеристики резидентного программного обеспечения микроконтроллеров

Рассмотрим данный вопрос на примере контроллера программируемого универсального (КПУ) “Электроника МС2721”. КПУ выполнен на основе КР580ВМ80А. Резидентное программное обеспечение КПУ состоит из программы “монитор”, набора тестовых программ и библиотеки подпрограмм обработки чисел с плавающей точкой.

Рассмотрим программу “монитор”. Она обеспечивает диалоговый режим работы оператора с КПУ и обеспечивает следующие режимы работы:

1. Управление выполнением программ

2. Управление обменом информации с внешними устройствами

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.