|

D7-D0 |

I/O |

шина данных |

|

CS |

I |

выбор кристала |

|

A0 |

I |

младший разряд шины адреса |

|

RD |

I |

чтение регистров |

|

WR |

I |

запись в регистры |

|

CLK |

I |

синхронизация |

|

LPEN |

I |

Light Pen - сигнал от светового пера |

|

INTR |

O |

Запрос Прерывания, формируется при выводе последнего символа в кадре |

|

DREQ |

O |

DMA Request |

|

CC6 - СС0 |

O |

6-ти разрядные коды символов |

|

LC3 -LC0 |

O |

Line Counter Output |

|

LA1, LA0 |

O |

Line Attribute |

|

GPA1, GPA0 |

O |

General Purpose Attribute |

|

VSP |

O |

Video Suppress |

|

HLGT |

O |

High Light - подсветка |

|

RVV |

O |

Reverce Video |

|

HRTC |

O |

Horisontal Retrance |

|

VRTC |

O |

Vertical Retrance |

|

LTEN |

O |

Light Enable - разрешение светового пера |

|

42. Функциональные возможности арифметического сопроцессора К1810ВМ87. Программная модель, форматы обрабатываемых данных. Анализ ситемы команд.

Сопроцессор может быть использован только совместно с центральным сопроцессором ВМ861ВМ88, так как в нем отсутствует механизм выборки команд. Сопроцессор предназначен для повышения производительности центрального процессора в среднем в 100 раз при выполнении операций с многоразрядными целыми и вещественными числами. Сопроцессор содержит 4 16-битовых, один 64-битовый и 8 80-битовых регистров. Он имеет 16-битную шину данных для связи с ОЗУ и портами ввода-вывода, отображенными на память. Шина адреса имеет 20 линий, что позволяет при передаче данных непосредственно адресоваться к памяти емкостью до 1 Мбайта.

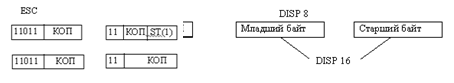

Система команд:

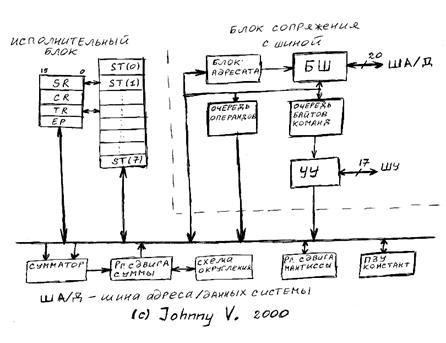

ST(i) – арифм. регистры

Двоичные целые числа

· Слово (16-разр. число со знаком)

· Короткое целое (32 со знаком)

· Длиное целое (64 со знаком)

В память целые числа записываются начиная с младшего байта.

Двоично-десятичные:

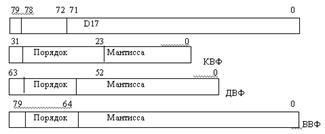

D17 – D0 – 4-разрядные коды цифр числа. Т.е. максимальное число значащих разрядов – 18.

Для записи двоично-десятичных чисел в памяти отводится 10 байт. Старший байт содержит лишь только знак числа в старшем бите, остальные разряды не используются.

Вещественные числа.

Могут быть представлены в трех вариантах:

КВФ – короткий вещественный формат, занимает 32 разряда и состоит из 23-разрядной мантиссы, 8-разрядов порядка и знака мантиссы.

ДВФ – длинный ВФ, 64 разряда, состоит из 52-разрядной мантиссы, 11 разрядов порядка и знака мантиссы.

ВВФ – вещественный ВФ, занимает 80 разрядов, состоит из 64-разрядной мантиссы, 15-разрядного порядка и знака мантиссы.

|

54.

Алгоритм псевдо - LRU действует следующим образом. Когда в цикле считывания происходит промах и в кэш-память необходимо передать из памяти новую строку, приходится выбирать для заполнения одну из четырех строк множества. Если в множестве есть недостоверная строка (ее бит достоверности содержит 0), то для заполнения выбирается именно эта строка. Когда же все строки в множестве достоверны (все 4 бита достоверности содержат 1), заменяемая строка выбирается с привлечением бит из блока LRU.

Обозначим строки в множестве через LO, LI, L2 и L3. Каждому множеству в блоке LRU соответствуют три бита ВО, В1 и ВЗ, которые модифицируются при каждом попадании и заполнении следу-ющим образом:

- если последнее обращение в множестве было к строке LO или L1, то бит ВО устанавливается в состояние 1, а при обращении к строке L2 или L3 бит ВО сбрасывается в 0; ;

- если последнее обращение в паре LO-—L1 было к строке LO, то бит В1 устанавливается в состояние 1, а при обращении к строке L1 бит В1 сбрасывается в 0;

- если последнее обращение в паре L2—L3 было к строке L2, то бит В2 устанавливается в состояние 1, а при обращении к строке L3 бит В2 сбрасывается в 0.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.