#IOW и #IOR при обеспечении обмена работают как выходы, а при работе с внутренними регистрами - как входы.

DRQ - запрос от устройства, требующего прямого доступа к памяти. Могут восприниматься запросы от 4-х устройств. ВТ57 формирует из них общий (Hold Request). Приоритет - фиксированный или циклический (динамически менять приоритеты нельзя).

READY - получение готовности (например от памяти, если она медленная).

AEN - разрешение выдачи адреса во внешнюю среду.

ADSTB - выданный адрес фиксируется во внешнем регистре. Это необходимо, т.к. на адресных выходах этот адрес будет недолго.

TC - вывод завершен (завершение передачи блока).

HLDA - сигнал, выставляемый процессором, получившим запрос HRQ (подтверждение HOLDа)

Структура ВТ57:

ВТ57 содержит 10 программно доступных регистров. Это 4-х канальный контроллер; его основное назначение - формирование управляющих сигналов для обмена, подсчет циклов ПДП.

PR - Priority Resolver (“разрешатель” приоритетов).

MR - Mode Register (Регистр Режима)

CL - Control Logic (управляющая логика)

Ch - Channel (Канал).

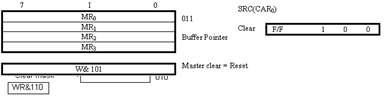

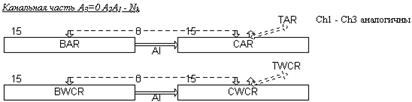

Программная модель

А3 = 1 Управляющая часть

A2A1= 00 - канал 0 D15D14=00 - контроль (без пересылок)

01 - канал 1 01 - запись

10 - канал 2 10 - чтение

11 - канал 3 11 - *

Каждый канал - 2 регистра. 1-й содержит адрес ячейки, с которой происходит обмен. 2-й подсчитывает количество циклов ПДП. 1-й регистр используется для записи начального адреса, а дальше микросхема работает в режиме автоинкремента. В сторону уменьшения ВТ57 работать не умеет (т.к. RG1 - суммирующий счетчик).

Во 2-м регистре для хранения количества циклов используются только разряды 0-13. Разряды 14-15 определяют тип обмена: контроль (без пересылок данных), запись или чтение. Существует триггер Flip/Flop, который определяет работу с младшим байтом счетчика текущего адреса. В ВТ57 этот триггер программно недоступен. В ВТ37 существуют команды его программирования. Регистр-счетчик циклов ПДП организован как вычитающий счетчик.

Программная модель

А3 = 1 Управляющая часть

|

|

Примеры программирования:

1) Запись, ручное управление:

|

MVI A,00 OUT D4 MVI A,0D OUT D4 MVI A,10 OUT D5 MVI A,40 OUT D5 MVI A,44 OUT D8 RST 1 |

2) Чтение, ручное управление: MVI A,00 OUT D6 MVI 0D OUT D6 MVI A,07 OUT D7 MVI A,80 OUT D7 MVI A,08 OUT D8 RST 1 |

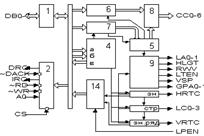

37. Структура программируемого контроллера ЭЛТ КР580ВГ75 ( I-8275 ). Форматы команд и специальных управляющих кодов.

Элементы структуры: 1)буффер шины

данных, 2)лог.схема чтения/записи/ПДП, 3)внутр. шина данных, 4)входная буфф.

схема-контроллер, 6,7)два буфф. ЗУ 80х8 на один знакоряд и сопряженные с ними

FIFO-стеки 16х7, 8)выходная схема-контроллер, 9)схема растровой синх-ии и

управления видеосигналом, счетчик - 7 разрядов (столбцы), счетчик - 6 разрядов

(строки), счетчик - 4 разряда (подсчет строк одного знакоместа), 14)два

регистра светового пера.

Элементы структуры: 1)буффер шины

данных, 2)лог.схема чтения/записи/ПДП, 3)внутр. шина данных, 4)входная буфф.

схема-контроллер, 6,7)два буфф. ЗУ 80х8 на один знакоряд и сопряженные с ними

FIFO-стеки 16х7, 8)выходная схема-контроллер, 9)схема растровой синх-ии и

управления видеосигналом, счетчик - 7 разрядов (столбцы), счетчик - 6 разрядов

(строки), счетчик - 4 разряда (подсчет строк одного знакоместа), 14)два

регистра светового пера.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.