);

TRUTH_TABLE

M :: [Q2..Q0];

0 :: [Q2..Q0].+.1;

1 :: [Q1,Q0,D];

END TRUTH_TABLE;

END CT_RG_TRUTH;

PROCEDURE CT_RG_STATE (

INPUT M, D, C, R ;

OUTPUT Q0, Q1, Q2 CLOCKED_BY /C RESET_BY R;

);

STATE_MACHINE CT_RG STATE_BITS [Q2..Q0];

STATE S0: IF M = 0 THEN GOTO S1; ELSIF D = 0 THEN GOTO S0; ELSE GOTO S1; END IF;

STATE S1: IF M = 0 THEN GOTO S2; ELSIF D = 0 THEN GOTO S2; ELSE GOTO S3; END IF;

STATE S2: IF M = 0 THEN GOTO S3; ELSIF D = 0 THEN GOTO S4; ELSE GOTO S5; END IF;

STATE S3: IF M = 0 THEN GOTO S4; ELSIF D = 0 THEN GOTO S6; ELSE GOTO S7; END IF;

STATE S4: IF M = 0 THEN GOTO S5; ELSIF D = 0 THEN GOTO S0; ELSE GOTO S1; END IF;

STATE S5: IF M = 0 THEN GOTO S6; ELSIF D = 0 THEN GOTO S2; ELSE GOTO S3; END IF;

STATE S6: IF M = 0 THEN GOTO S7; ELSIF D = 0 THEN GOTO S4; ELSE GOTO S5; END IF;

STATE S7: IF M = 0 THEN GOTO S0; ELSIF D = 0 THEN GOTO S6; ELSE GOTO S7; END IF;

END CT_RG;

END CT_RG_STATE;

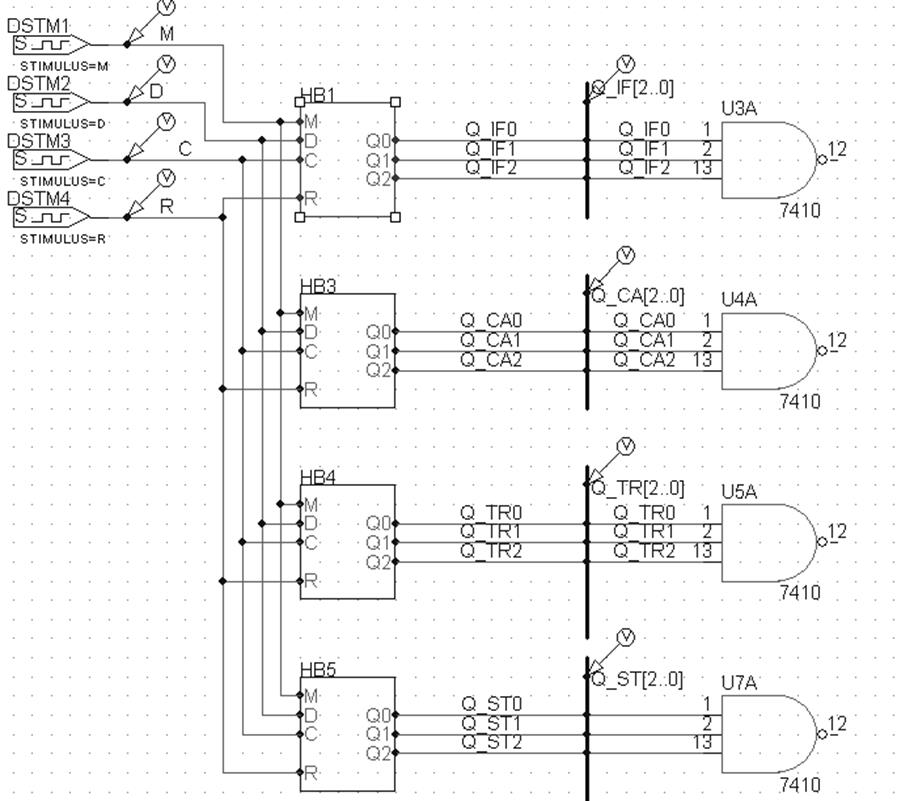

На рис.9 приведена схема верификации, а на рис. 10 результаты работы.

Рис. 9

Рис. 10

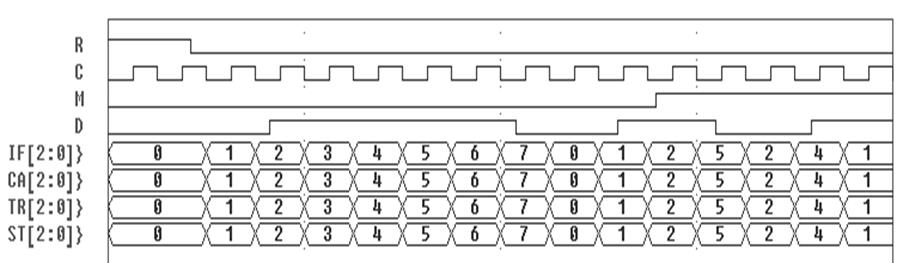

7. Потоковая DSL-модель автомата

Ниже приведен текст потоковой DSL-модели. На рис. 11 приведена схема верификации. Иерархический блок преобразован в иерархический символ.

PROCEDURE POTOK (

INPUT M, D, C, R ;

OUTPUT Q0, Q1, Q2 ;

);

JK_FLOP TT0, TT1, TT2 CLOCKED_BY /C RESET_BY R;

TT0.J = /((/D)*M);

TT0.K = /(D*M);

Q0 = TT0;

TT1.J = Q0;

TT1.K = Q0(+)M;

Q1 = TT1;

TT2.J = (M*Q1)+(Q1*Q0);

TT2.K = (Q1*Q0*(/M))+(M*(/Q1));

Q2 = TT2;

END POTOK;

Рис. 11

Результаты такие же как и на рис. 4.

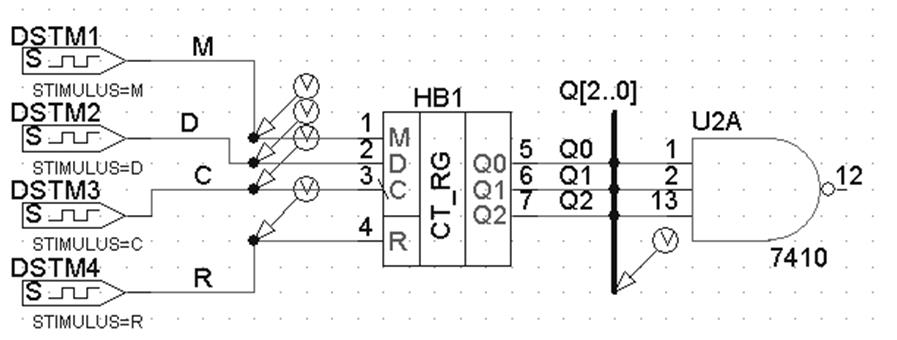

8. Синтез комбинационной части автомата на мультиплексорах

В этой части работы использованы два типа мультиплексоров: 8 в 1 и 4 в 1. Их УГО можно увидеть на рис. 12, DSL-модели приведены ниже.

PROCEDURE MUX4 (

INPUT D0, D1, D2, D3, A1, A2 ;

OUTPUT Y ;);

TRUTH_TABLE

[A2,A1] :: Y;

0 :: D0;

1 :: D1;

2 :: D2;

3 :: D3;

END TRUTH_TABLE;

END MUX4;

PROCEDURE MUX8 (

INPUT D0, D1, D2, D3, D4, D5, D6, D7, A1, A2, A4 ;

OUTPUT Y ;);

TRUTH_TABLE

[A4, A2, A1] :: Y;

0 :: D0;

1 :: D1;

2 :: D2;

3 :: D3;

4 :: D4;

5 :: D5;

6 :: D6;

7 :: D7;

END TRUTH_TABLE;

END MUX8;

Синтез комбинационной части на мультиплексорах заключается в следующем: на селектирующие входы мультиплексора подаются переменные, от которых зависят функции возбуждения триггеров, а на информационные логический ноль или логическая единица на каждый. При этом используются таблицы 5, 6, 7. Например при комбинации M=0 D=0 на J0 должна податься «1», поэтому на нулевой вход мультиплексора 4 в 1 подаем уровень логической «1», которая приданной комбинации появится на выходе мультиплексора. Ниже приведена схема верификации схемы с комбинационной частью на мультиплексорах.

Рис. 12

Результаты работы аналогичны результатам, представленным на рис. 4.

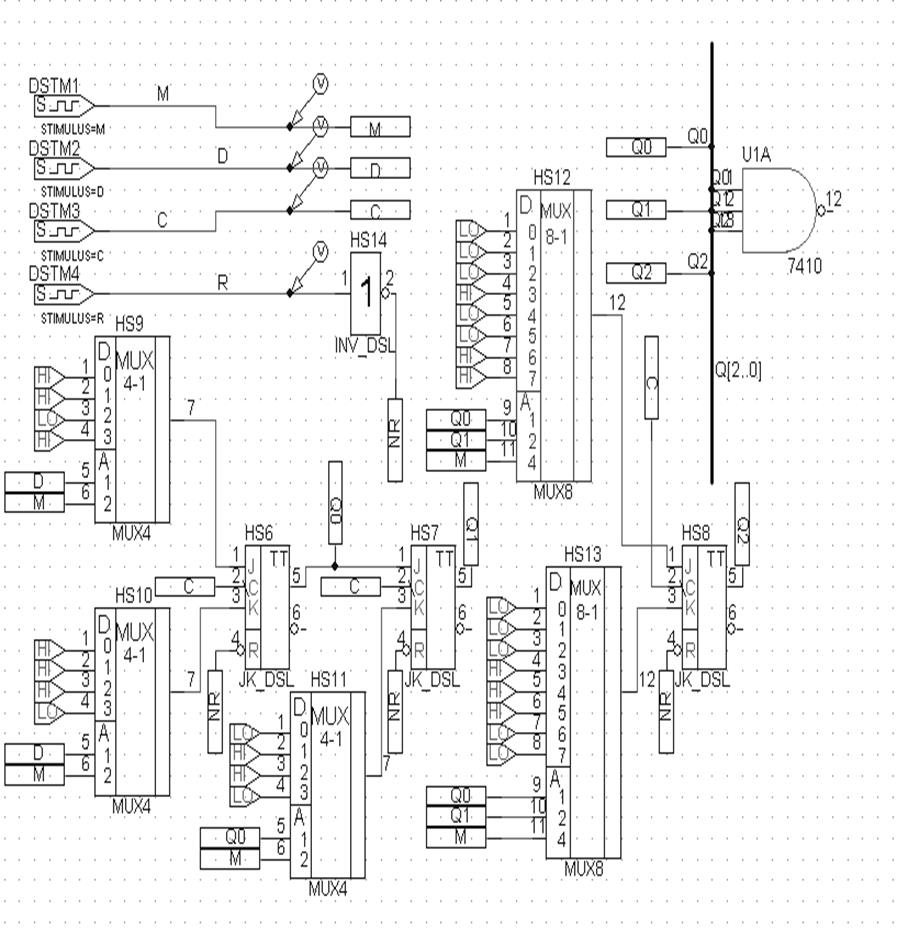

9. Синтез комбинационной части автомата на дешифраторах

Здесь принцип следующий: на входы дешифратора подаются переменные, от которых зависят функции возбуждения обеих входов триггеров. На выходе ставиться вентиль типа ИЛИ, который будет «ловить» единицы, которые нам нужны. На примере таблицы 5 на J0 нужно подавать 1 при комбинации M D равной 00, 01, 11. Соответственно 0, 1, 3 выходы дешифратора 2 в 4 подключаем к вентилю 3ИЛИ. Теперь если на входах будет одна из нужных комбинации, то на J0 поступит 1, иначе 0. Данный пример демонстрирует рис 13., на котором изображена схема верификации.

Ниже приведены DSL-модели дешифраторов 2 в 4 и 3 в 8.

PROCEDURE DC2_4 ( INPUT D1, D2 ;

OUTPUT O0, O1, O2, O3 ;);

TRUTH_TABLE

[D2,D1] :: [O3..O0];

0 :: 1;

1 :: 2;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.