|

MQ1/Q0 |

0 |

1 |

|

00 |

0 |

0 |

|

01 |

0 |

1 |

|

11 |

0 |

0 |

|

10 |

1 |

1 |

|

MQ1/Q0 |

0 |

1 |

|

00 |

0 |

0 |

|

01 |

0 |

1 |

|

11 |

1 |

1 |

|

10 |

0 |

0 |

В таблицах 8 и 9 представлены

карты Карно для J2 и K2 соответственно. Получается следующее: ![]() и

и ![]() .

.

Схема автомата с комбинационной частью будет приведена немного позже (когда будут разрабатываться иерархические символы).

3. Проектирование структурной DSL-модели автомата.

Ниже располагается текст структурной DSL-модели автомата.

USE 'ELEM_FOR_STRUCT';

PROCEDURE STRUCT (

INPUT M, D, C, R ;

OUTPUT Q0, Q1, Q2;

);

NODE NM, ND, NR, J0, K0, K1, J2, K2, F1, NQ0, NQ1, NQ2;

HS1: INV_DSL(R, NR);

HS2: INV_DSL(D, ND);

HS3: INV_DSL(M, NM);

HS4: NAND2_DSL(ND, M, J0);

HS5: NAND2_DSL(D, M, K0);

HS6: XOR2_DSL(M, Q0, K1);

HS7: JK_DSL(J0, C, K0, NR, Q0, NQ0);

HS8: JK_DSL(Q0, C, K1, NR,Q1, NQ1);

HS9: AND2_2_OR2_DSL(M, Q1, Q1, Q0, J2);

HS10:AND2_DSL(Q0, Q1, F1);

HS11:AND2_2_OR2_DSL(NM, F1, M, NQ1, K2);

HS12:JK_DSL(J2, C, K2, NR, Q2, NQ2);

END STRUCT;

Модели элементов располагаются в файле ELEM_FOR_STRUCT.DSL, вот его содержание:

PROCEDURE AND2_2_OR2_DSL(

INPUT IN1,IN2,IN3,IN4;

OUTPUT OUT1;);

OUT1 = (IN1*IN2)+(IN3*IN4);

END AND2_2_OR2_DSL;

PROCEDURE XOR2_DSL(

INPUT IN1,IN2;

OUTPUT OUT1;);

OUT1 = IN1(+)IN2;

END XOR2_DSL;

PROCEDURE INV_DSL(

INPUT IN1;

OUTPUT OUT1;);

OUT1 = /IN1;

END INV_DSL;

PROCEDURE NAND2_DSL(

INPUT IN1,IN2;

OUTPUT OUT1;);

OUT1 = /(IN1*IN2);

END NAND2_DSL;

PROCEDURE AND2_DSL(

INPUT IN1,IN2;

OUTPUT OUT1;

); OUT1 = IN1*IN2;

END AND2_DSL;

PROCEDURE JK_DSL(

INPUT J,C,K,R;

OUTPUT Q, NQ;);

JK_FLOP F CLOCKED_BY /C RESET_BY /R;

F.J = J; F.K = K;

Q = F; NQ = /F;

END JK_DSL;

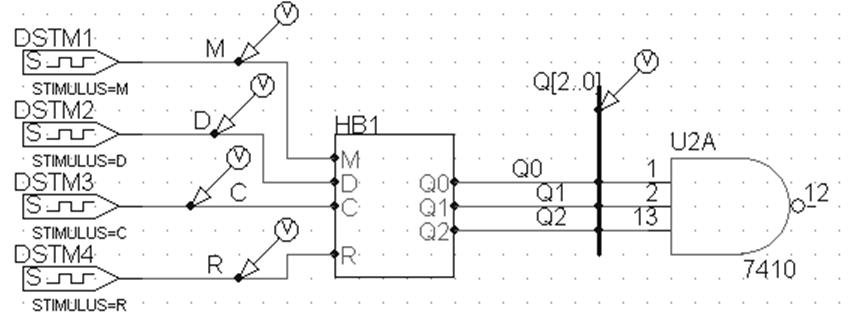

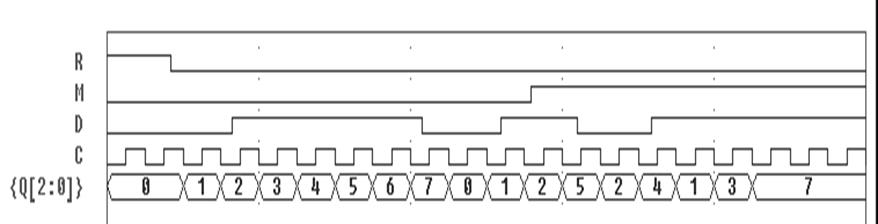

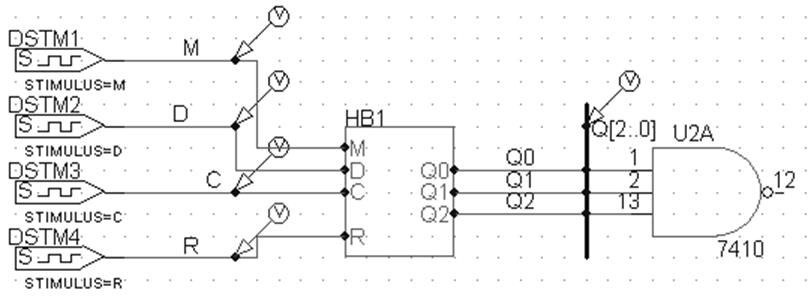

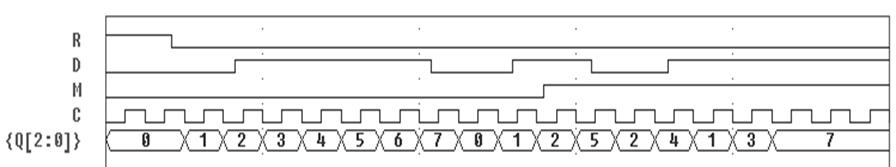

Схема верификации иерархического блока со структурной DSL-моделью представлена на рис. 3, а результат работы на рис. 4.

Рис. 3

Рис. 4

4. Проектирование иерархических символов для своей схемы.

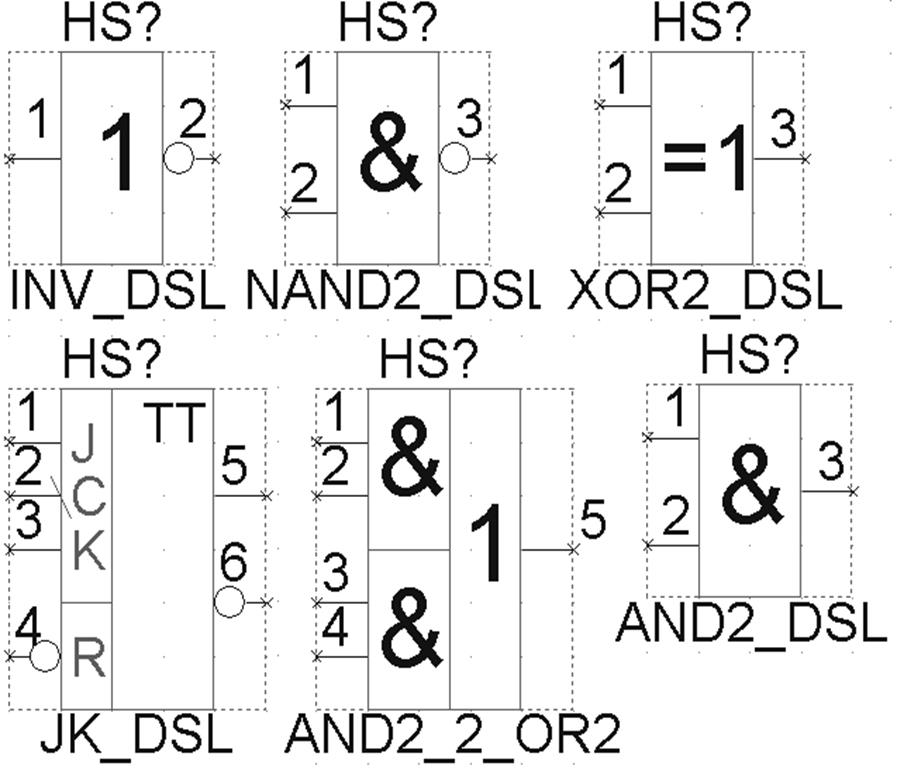

Ниже на рис. 5 представлены иерархические символы (а если быть точнее – их УГО) для проектируемой схемы. А их DSL-модели были приведены при проектировании структурной DSL-модели.

Рис. 5

Хочу заметить (хотя стоило сделать это ранее), что для

возбуждения ![]() я не использовал элемент 3И, так как это

бы потянуло использование 2ИЛИ, вместо этого получился неплохой симбиоз

элементов 2-2И-2ИЛИ и 2И, так как 2-2И-2ИЛИ уже использовался до этого для

входа другого триггера и не было смысла придумывать кучу других элементов.

я не использовал элемент 3И, так как это

бы потянуло использование 2ИЛИ, вместо этого получился неплохой симбиоз

элементов 2-2И-2ИЛИ и 2И, так как 2-2И-2ИЛИ уже использовался до этого для

входа другого триггера и не было смысла придумывать кучу других элементов.

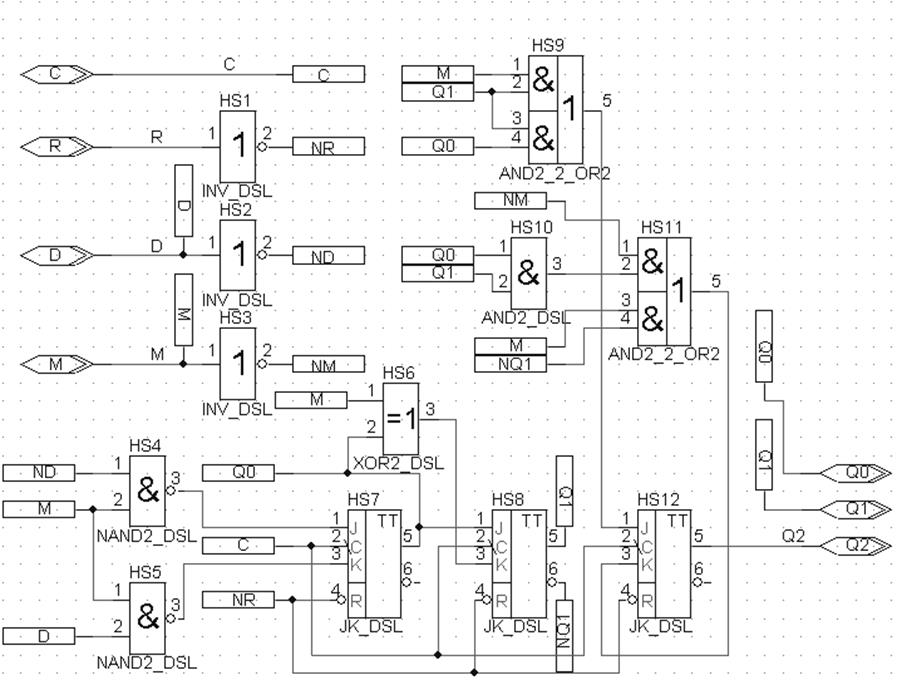

5. Проектирование иерархического блока со схемой замещения на ранее созданных иерархических символах.

На рис. 6 представлена схема замещения на иерархических символах, на рисунке 7 – схема верификации, а на рисунке 8 – результаты работы.

Рис.6

Рис.7

Рис.8

6. Поведенческая DSL-модель цифрового автомата с любой комбинацией операторов.

Ниже приведен текст поведенческих DSL-моделей (все комбинации операторов).

PROCEDURE CT_RG_IF (

INPUT M, D, C, R ;

OUTPUT Q0, Q1, Q2 CLOCKED_BY /C RESET_BY R;

);

IF M = 0 THEN [Q2..Q0] = [Q2..Q0].+.1;

ELSE [Q2..Q0] = [Q1,Q0, D];

END IF;

END CT_RG_IF;

PROCEDURE CT_RG_CASE (

INPUT M, D, C, R ;

OUTPUT Q0, Q1, Q2 CLOCKED_BY /C RESET_BY R;

);

CASE M

WHEN 0 => [Q2..Q0] = [Q2..Q0].+.1;

WHEN 1 => [Q2..Q0] = [Q1,Q0, D];

END CASE;

END CT_RG_CASE;

PROCEDURE CT_RG_TRUTH (

INPUT M, D, C, R ;

OUTPUT Q0, Q1, Q2 CLOCKED_BY /C RESET_BY R;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.