Министерство высшего и профессионального образования РФ

«Разработка ядра микроЭВМ»

Факультет: АВТ.

Группа: АМ – 811

Студент: Грибенников А.А.

Преподаватель: Соболев В.И.

Новосибирск 2001

Содержание.

Введение…………………………………………………………….……

1. Цель разработки и исходные данные………………………………..

1.1 Цель разработки……………………………………………………….

1.2 Общие исходные данные…………………………………………….

1.3 Индивидуальные исходные данные………………………………..

2. Форматы команд…………………………………………………………

3. Разработка операционного блока…………………………………….

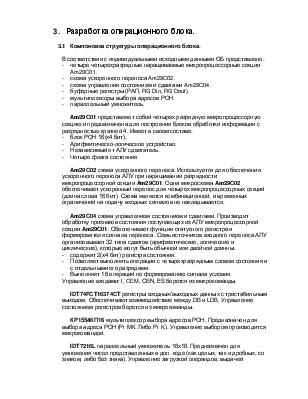

3.1 Компоновка структуры ОБ……………………………………………

3.2 Структурная схема ОБ………………………………………………..

3.3 Описание работы ОБ…………………………………………………

3.4 Расчет времени цикла ОБ……………………………………………

4. Разработка микропрограммного устройства управления…….….

4.1 Компоновка структуры МУУ………………………………………….

4.2 Структурная схема МУУ……………………………………………...

4.3 Описание работы МУУ………………………………………………..

4.4 Расчет времени цикла МУУ………………………………………….

5. Формат микрокоманды…………………………………………………

6. Разработка памяти………………………………………………………

6.1 Компоновка структуры памяти………………………………………

6.2 Структурная схема памяти…………………………………………..

6.3 Описание работы памяти…………………………………………….

6.4 Разработка функциональной схемы памяти……………………...

6.5 Функциональная схема памяти……………………………………..

6.6 Расчет времени доступа к памяти………………………………….

7. Разработка схемы синхронизации……………………………………

8. Разработка блока начальной установки…………………………….

Заключение……………………………………………………………….

Список литературы……………………………………………………...

Данная курсовая работа выполнена по курсу Схемотехника с надеждой

на приобретение первого опыта проектирования цифровых устройств.

Об’ектом разработки является прототип ядра микропроцессора содержащий минимальный набор устройств (операционный блок, микропрограммное устройство управления, основная память и блок синхронизации).

Проектирование операционного блока и устройства управления

ведется на структурном уровне, в отличие от памяти и блока синхронизации, разработка которых заканчивается электрическими принципиальными схемами.

1. Цели разработки и исходные данные.

1.1 Цели разработки:

Задача данной курсовой работы заключается в разработке ядра процессора микроЭВМ основные требования которого:

· высокое быстродействие (производительность);

· простота и надежность схемных решений.

Необходимо также обеспечить отсутствие в схемах критических временных соотношений, риска сбоя и гонок сигналов, использование унифицированных способов обмена между устройствами.

1.2 Общие исходные данные:

В состав разрабатываемого об’екта входят: операционный блок, микропрограммное устройство управления, запоминающие устройства, реализующие функции основной памяти и интерфейсные элементы, обеспечивающие информационную и электрическую совместимость между ними.

1.3 Индивидуальные исходные данные:

Процессорный модуль Am29C01 16 бит

+ схемная поддержка операции умножения

Секвенсер МК Am29C10 12 бит

Основная память SRAM 16kb

EEPROM 4kb

2. Форматы команд.

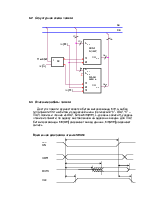

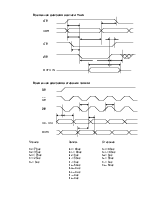

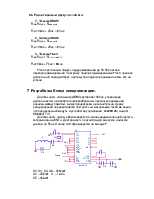

Поддерживаются как 16-ти, так и 32-х разрядные команды.

16-ти разрядная команда состоит из поля команды (крайний левый байт), где находится код операции, за которым следует два 4-х разрядных поля, определяющих адреса используемых в команде РЗУ.

32-х разрядная команда состоит из двух слов. Первое из которых полностью соответствует 16-ти разрядной команде. Второе же представляет собой

16-ти разрядную величину, которая является непосредственно, либо адресом ячейки памяти, либо данными.

Команда «регистр - регистр»

|

15 8 7 4 3 0

КОП – код операции;

R1 – регистр приемник;

R2 – регистр источник.

15 8 7 4 3 0

КОП – код операции;

Х – регистр содержащий адрес памяти;

R2 – регистр источник.

Команда ветвления.

|

КОП – код операции

АП – адрес перехода.

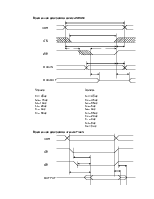

Команда «регистр - индексируемая память»

|

31 24 23 20 19 16

|

15 0

КОП – код операции;

Х1 – регистр содержащий адрес ячейки памяти;

R2 – регистр источник/приемник;

d - смещение.

Команда «регистр – память – непосредственные данные»

|

31 24 23 20 19 16

|

15 0

КОП – код операции;

Х1 – регистр содержащий адрес ячейки памяти;

R2 – регистр приемник;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.