![]()

![]()

![]()

![]() DATA IN

DATA IN

Временная диаграмма стирания памяти

![]()

![]() __

__

OE

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() __

__

![]()

![]() CE

CE

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() __

__

WE

|

|||

|

|||

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() A0 - A14

A0 - A14

|

![]() DATA

DATA

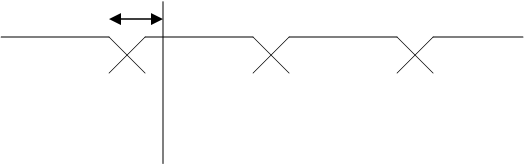

Чтение Запись Стирание

tCE= 70нс tWP= 90нс tWP= 90нс

tOE= 35нс tWPH= 90нс tWPH= 90нс

tACC= 70нс tAS= 0нс tAS= 0нс

tDF= 25нс tAH= 50нс tAH= 50нс

tOH= 0нс tDH= 0нс tDH= 0нс

tDS= 50нс tDS= 50нс

tOES= 0нс

tOEH= 0нс

tCH= 0нс

tCS= 0нс

6.4 Разработка функциональной схемы памяти

При монтаже микросхем памяти, необходимо учитывать рекомендации фирм производителей по установке и подключению микросхем, на плату. Схемы подключения взяты из документации по данным микросхемам.

CY7C148 - 45 AT49F516 - 70

6.6 Расчет времени доступа к памяти

1. Чтение SRAM

ТцМ=ТздDC + Тread cycle

ТцМ = 18нс + 45нс = 63 нс.

2. Запись SRAM

ТцМ=ТздDC + Тwrite cycle

ТцМ = 18нс + 45нс = 63 нс.

3. Чтение Flash

ТцМ=ТздDC + ТADR->DataOUT

ТцМ=18нс + 70нс = 88 нс.

Flash постоянная, память поддерживающая до 10.000 циклов перепрограммирования. Поскольку перепрограммирование Flash, процесс длительный, порядка 10сек, поэтому при подсчете времени цикла, это не учтено.

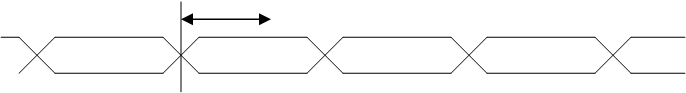

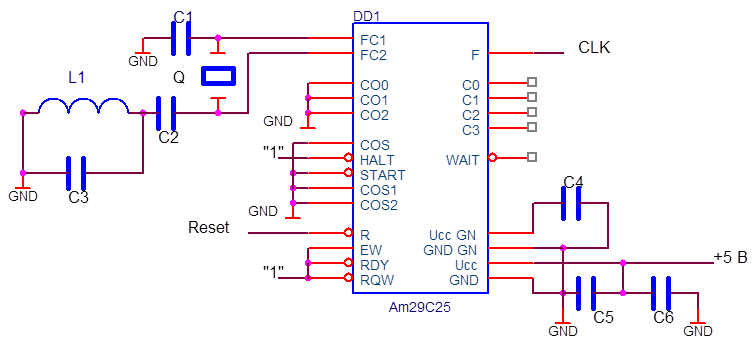

7 Разработка блока синхронизации.

Длительность цикла микроЭВМ составляет 100нс, управление длительностью не является целесообразным, поскольку временная разница между памятью, микропроцессором не значительна. Схему синхронизации предполагается построить на микросхеме такой же серии, что процессорный модуль и устройство управления, Am29C25 ( аналог КМ1804ГГ1 ).

Длительность цикла, обеспечивается 2-мя периодами опорной частоты, которая равна 20МГц. Длительность полуцикла для высокого и низкого уровня, по 50нс. Сигнал CLK формируется на выходе F.

С1, С3, С4, С6 – 1000пФ

С2 – 256пФ L1 – 1мкГн

С5 – 10мкФ

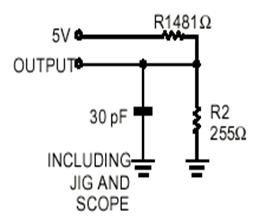

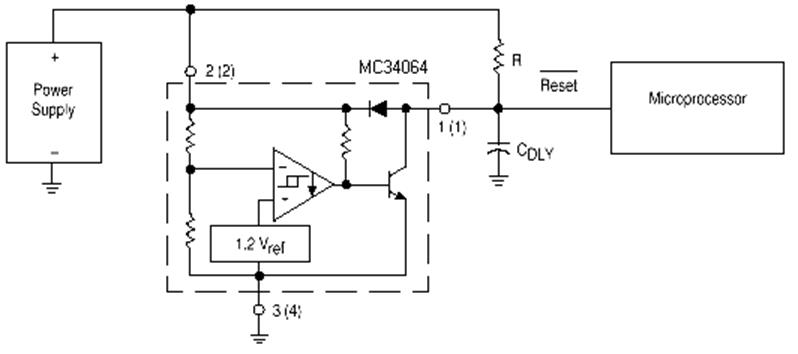

8. Разработка блока начальной установки

Схема начальной установки основана на микросхеме контроллера начальной предустановки,MC34064, фирмы Motorola

Схема начальной установки.

|

Длительность сигнала начальной установки схемы, рекомендовано делать не менее 500нс. Длительность сигнала рассчитывается по формуле: T=R*CDLY*Ln (Uип/(Uип-Uпор)).

Такая длительность достигается при значениях: R=10 КОм, CDLY=100пФ.

Заключение.

В результате выполнения курсовой работы, было разработано ядро процессора микроЭВМ, на основе микропроцессорной секции Am29C01 и секвенсера микрокоманд Am29C10 и достигнуты, надежность схемных решений и хорошее быстродействие, на данных компонентах. В обвязке процессорного модуля и секвенсера микрокоманд, использовалась элементная база, производства, как ближнего, так и дальнего зарубежья.

Список литературы:

1. Схемотехника. Руководство к курсовой работе. :

- Новосибирск.: 1997г. – 62стр.

2. Петровский И.И. Логические ИС КР1533, КР1554: справочник

Часть I,II. М.: Бином, 1993г.

3. Цифровые и аналоговые интегральные микросхемы : справочник. Под ред. Якубовского С.В. – М.: Радио и связь, 1989. – 496стр.

4. Угрюмов Е.П. Проектирование элементов и узлов ЭВМ : Учебник пособие для ВУЗов – М.: Высшая школа, 1987г. – 318стр.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.