Расчетное время цикла МУУ = 95 нс. Время цикла ОБ = 98.2 нс. При времени такта, равным 100 нс. Выполняется согласование длительности циклов ОБ и МУУ, поэтому время цикла примем равным 100 нс.

6. Разработка памяти

6.1 Компоновка структуры памяти

В соответствии с индивидуальными данными память состоит из:

ОЗУ SRAM – 16K и ПЗУ EEPROM – 4K, с возможностью электрического стирания информации. Но, из-за безрезультатных поисков, микросхем памяти EEPROM, удовлетворяющих временным параметрам разрабатываемой структуры, пришлось остановить выбор на микросхеме Flash памяти большего объема, которая, также, позволяет электрически стирать информацию, а объем памяти превышающий заданный, можно использовать для расширения памяти.

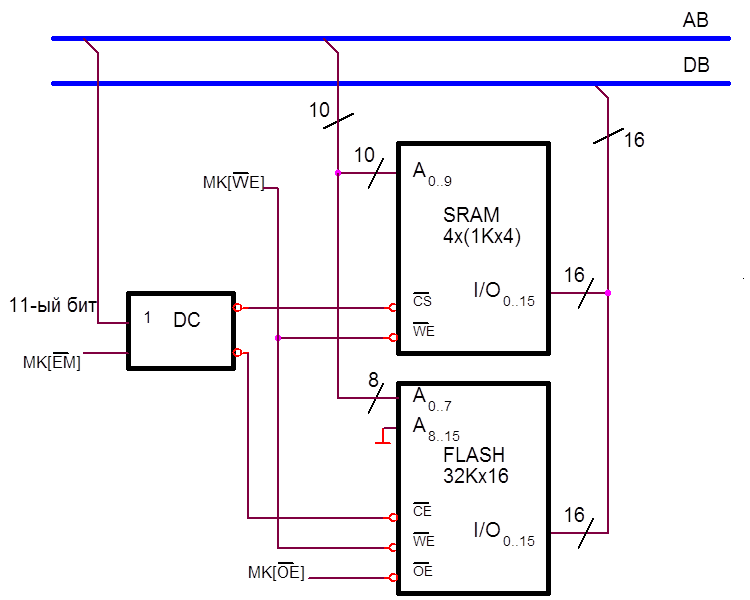

ОЗУ SRAM – выполнено на 4-х микросхемах CY7C148 – 45 фирмы CYPRESS, с организацией 1Kx4. ПЗУ Flash – на одной микросхеме AT49F516 – 70 фирмы ATMEL, с организацией 32Kx16.

В состав памяти также входит : К1533ИД7 – дешифратор-демультиплескор 3 на 8. Используемый для активизации нужного типа памяти (ОЗУ или ПЗУ).

Карта памяти

0000

![]() 0001

0001

![]() .

.

.

. SRAM

![]() 3FFF

3FFF

4000

![]() 4001

4001

![]() .

.

.

. Flash

4FFF

6.2 Структурная схема памяти

6.3 Описание работы памяти

Доступ к памяти осуществляется битом микрокоманды ME, а выбор типа памяти 11-тым битом из адресной шины (логический “0” - ОЗУ, “1” – ПЗУ). Запись и чтение из ОЗУ, битом MK[WE], L-уровень запись/H-уровень чтение из памяти, по адресу выставленном на адресных входах. Для ПЗУ, бит микрокоманды MK[OE] разрешает вывод данных, MK[WE] разрешает запись.

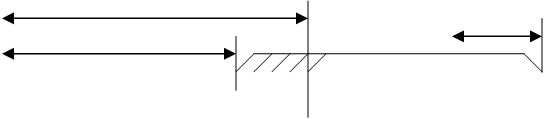

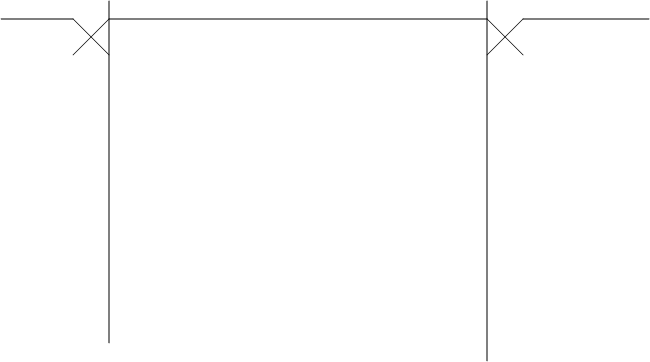

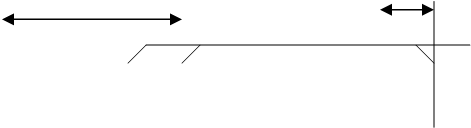

Временная диаграмма чтения SRAM

![]()

![]()

![]()

![]()

![]() ___

___

CS

ADR

|

|||||||

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() DATA

DATA

|

Vcc

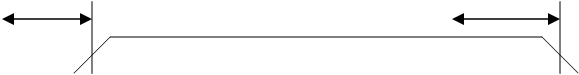

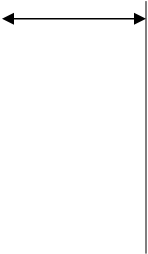

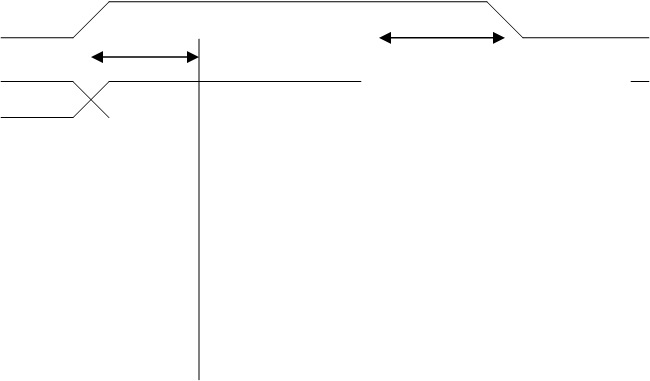

Временная диаграмма записи SRAM

|

ADR

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() __

__

![]()

![]()

![]()

![]()

![]() CS

CS

|

|

|||||||

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() __

__

![]() WE

WE

|

![]()

![]()

![]()

![]()

![]()

![]()

![]() Data IN

Data IN

|

|

||||||||

![]()

![]()

![]()

![]()

![]()

![]()

![]() Data OUT

Data OUT

Чтение Запись

tRC= 45нс tWC= 45нс

tACS= 15нс tCW= 45нс

tLZ= 10нс tAW= 35нс

tHZ= 20нс tWA= 5нс

tPU= 0нс tAS= 0нс

tPD= 30нс tWP= 35нс

tDW= 20нс

tDH= 0нс

tWZ= 8нс

tOW= 0нс

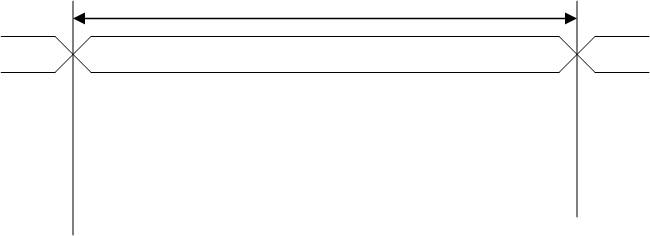

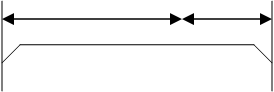

Временная диаграмма чтения Flash

|

![]()

![]()

![]() ADR

ADR

![]()

![]()

![]()

![]()

![]() __

__

![]() CE

CE

|

![]()

![]()

![]()

![]()

![]() __

__

![]()

![]()

![]()

![]() OE

OE

|

![]()

![]()

![]()

![]()

![]()

![]()

![]() OUTPUT

OUTPUT

Временная диаграмма записи Flash

![]()

![]() __

__

![]() OE

OE

ADR

![]()

![]()

![]()

![]()

![]() __

__

CE

![]()

![]()

![]() __

__

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]() WE

WE

|

|||||

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.