end VHD_block; --}} End of automatically maintained section

architecture VHD_block of VHD_block is

signal TEMP : std_logic_vector(3 downto 0); -- Переменные для хранения выходных данных

signal TEMP_CO : std_logic;

begin

process(CLK, LOAD, CTEN, D_U, D0, D1, D2, D3, TEMP,TEMP_CO)

begin

if (LOAD='0') then TEMP <= (D3,D2,D1,D0) after 17ns; --Режим загрузки. (Задержка после -- переключения сигнала LOAD равна 17ns)

elsif (CLK='1' and CLK'EVENT) then --По переднему фронту тактирующего сигнала

if(CTEN='0' and D_U='0') then --Режим прямого счета при D_U='0' TEMP <=TEMP+"0001" after 11ns; --с задержкой 11ns

elsif (CTEN='0' and D_U='1') then --Режим обратного счета при D_U='1'

TEMP<=TEMP-"0001" after 11ns; --с задержкой 11ns

end if;

end if;

if ((D_U='0' and TEMP = "1111") OR (D_U='1' and TEMP = "0000") ) then

TEMP_CO <= '1' after 25ns; --Условия переключения сигнала переноса

else TEMP_CO <= '0' after 25ns; --задержка при переключении равна 25ns

end if;

if (CTEN='0' and TEMP_CO ='1' and CLK ='0' ) then --Условия переключения сигнала на

--выходе наращивания счета

RCO <= '0' after 9ns; --задержка при переключении равна 9ns

else RCO <= '1' after 9ns;

end if;

end process;

CO<=TEMP_CO; --Присваивание значений временных

Q0<=TEMP(0); --переменных выходным сигналам

Q1<=TEMP(1);

Q2<=TEMP(2);

Q3<=TEMP(3);

end VHD_block;

14. Схема верификации.

Рис.23. Схема верификации проектируемого узла

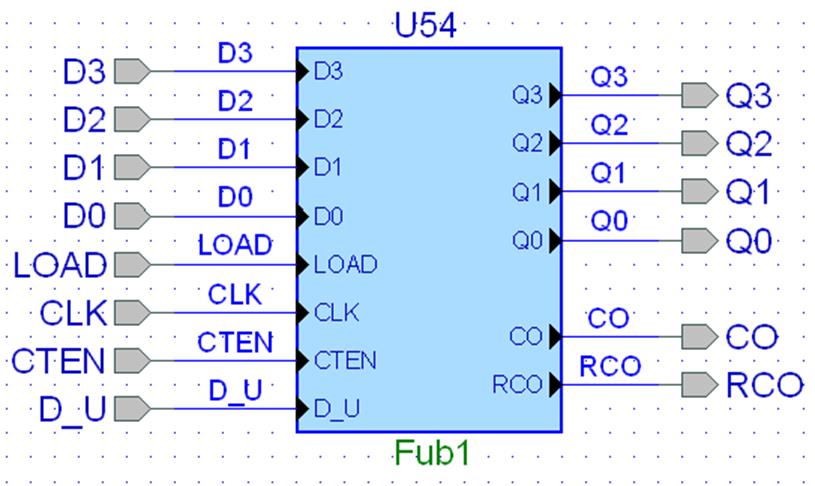

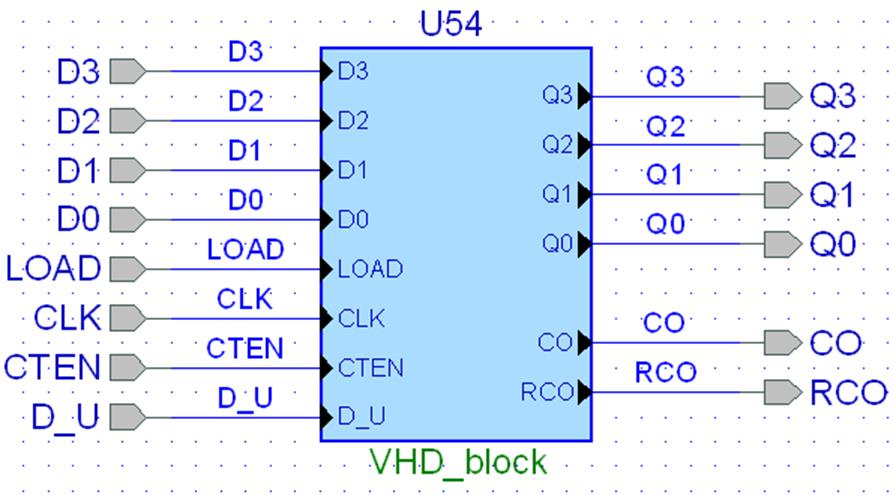

На схеме, представленной на Рис.23, изображено два символа. Первый из них (DD1) содержит иерархический блок (Рис.24.1), поддерживаемый схемой замещения (Рис.22). Второй (DD2) содержит иерархический блок (Рис.24.2), поддерживаемый VHDL – моделью, описанной в п.13.

Рис.24.1. Иерархический блок, поддерживаемый схемой замещения

Рис.24.2. Иерархический блок, поддерживаемый VHDL – моделью

15. Результаты моделирования.

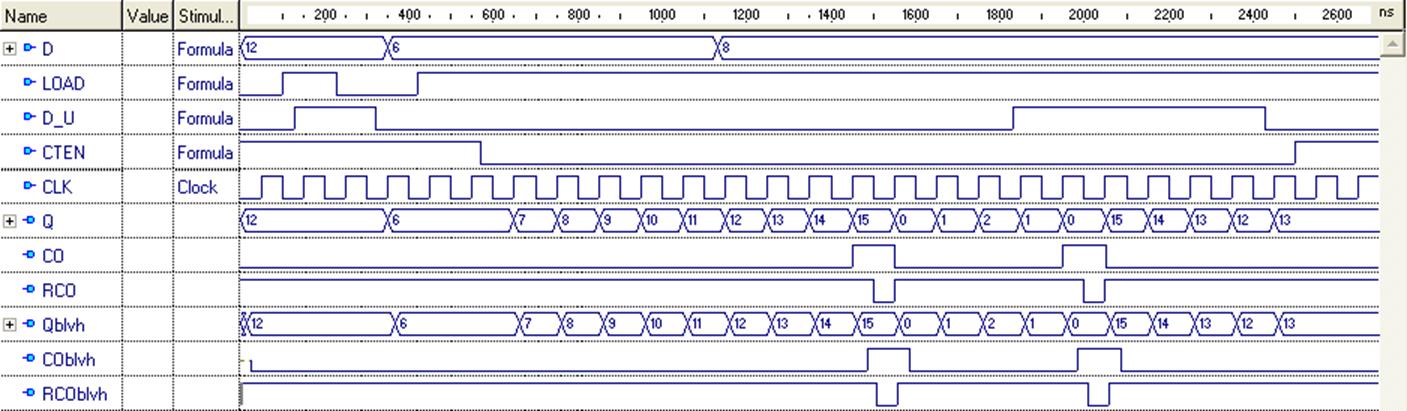

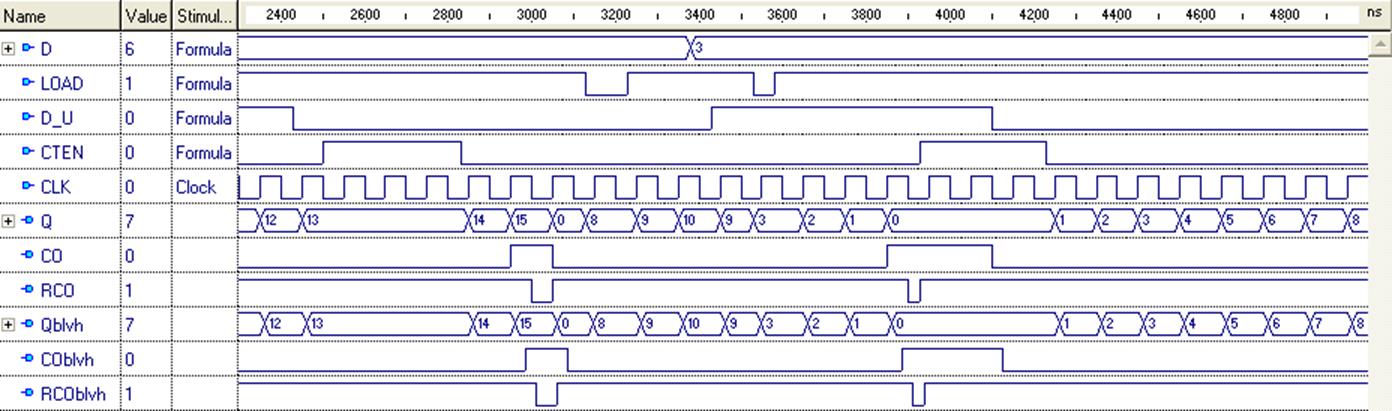

Как видно по временным диаграммам (Рис. 25.1, 25.2), при одинаковом наборе входных данных две схемы ведут себя схожим образом. Но в отличие от схемы замещения, в VHDL – модели предусмотрены задержки, поэтому все переключения на выходах элемента DD2 происходят несколько позже, чем на выходах элемента DD1.

|

|

|

|

|

|||||

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

|

||

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Рис. 25.1, 25.2. Временные диаграммы, полученные при моделирования схемы, представленной на рис.23 (начало, продолжение)

Выводы и личные впечатления.

Список литературы.

1. Микросхемы серии 1533 (Отраслевой руководящий документ): РД 11 0488.6-2004 – 248, 249 с.: ил.

2. Учебник по языку описания аппаратуры VHDL18.01.2014: (Составил А.В. Шалагинов) 28, 29 с

3. Журнал «Компоненты и технологии» № 2..9 от 2002 г., цикл статей «Знакомство с OrCAD 9.1» (автор А.В. Шалагинов)

4. Таблица соответствия отечественных и зарубежных микросхем найдена на сайте: http://www.integral.by/index.php?text_id=25

5. Описание микросхемы 74ALS191 найдено на сайте:

http://www.datasheetcatalog.com/datasheets_pdf/7/4/A/L/74ALS191.shtml

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.