Аналогичная помеха, возникающая на выходе СО, показана на Рис.7, но она не приводит к сбою в работе моделятора (так как не поступает на вход триггера).

|

Рис.7. Возникновение помехи из-за задержек при переключении сигналов на выходах

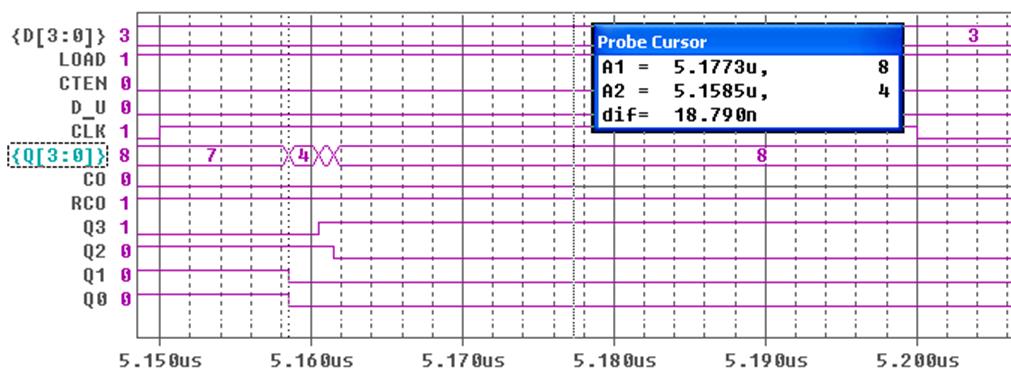

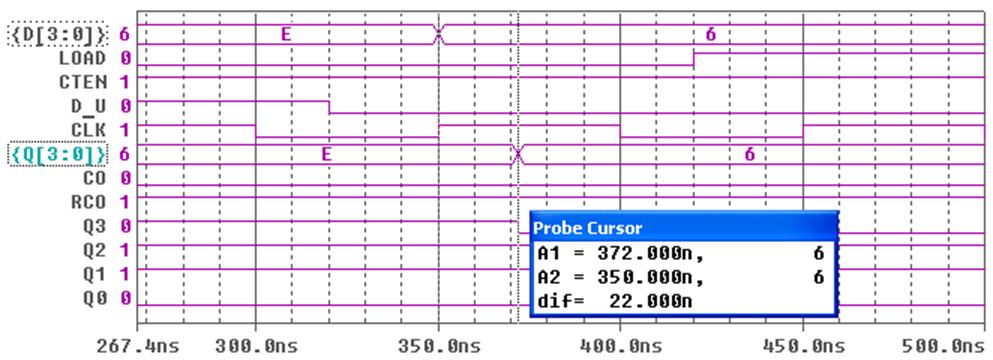

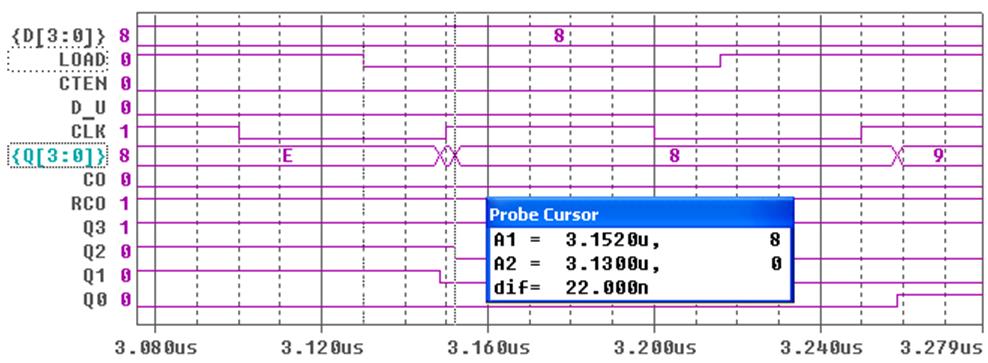

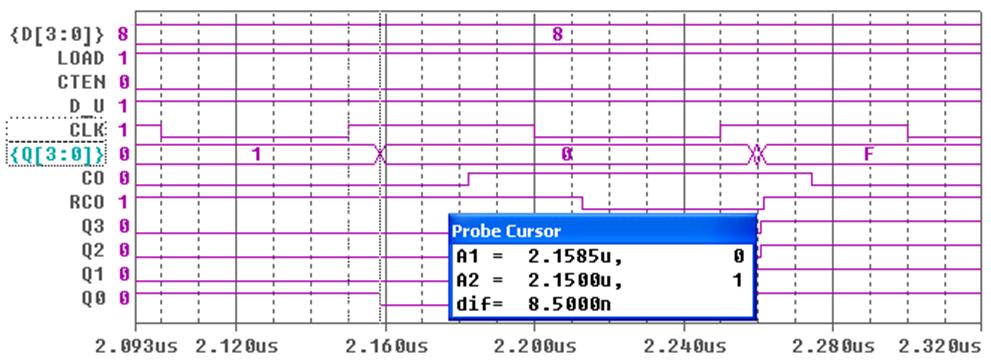

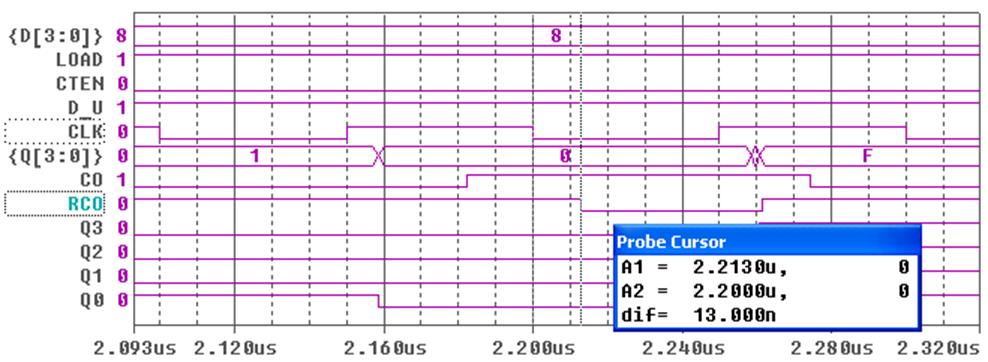

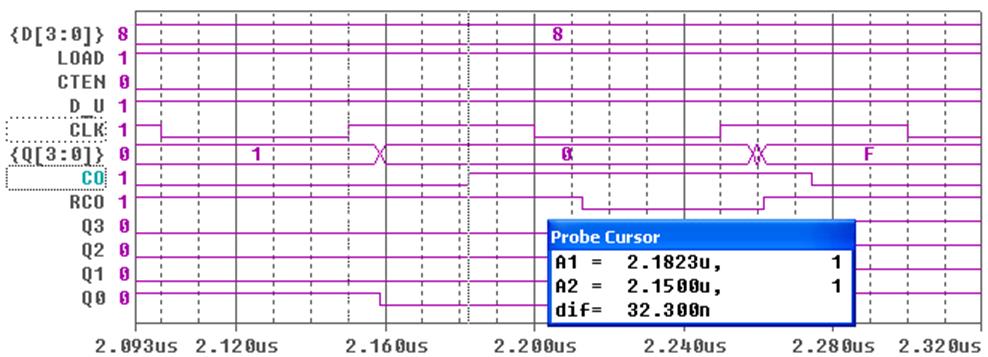

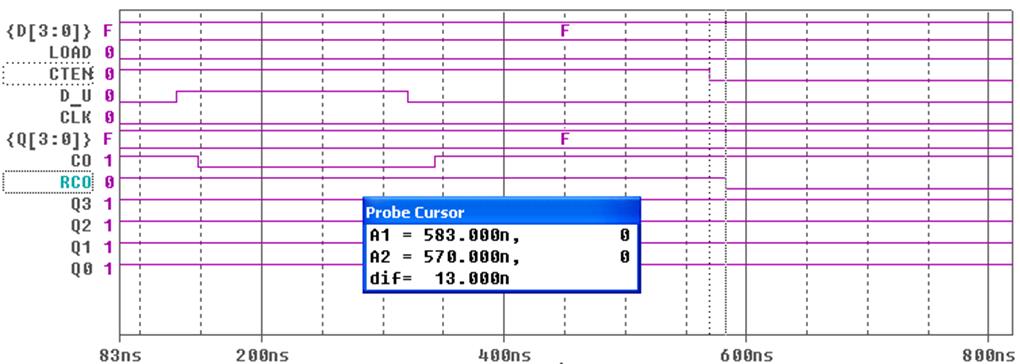

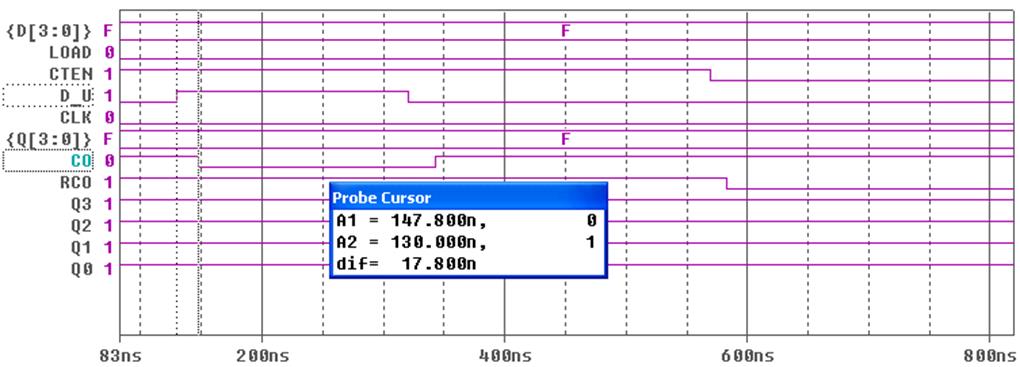

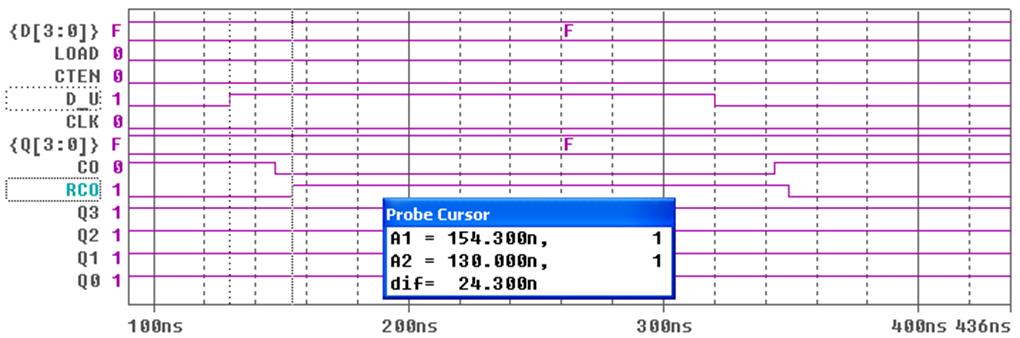

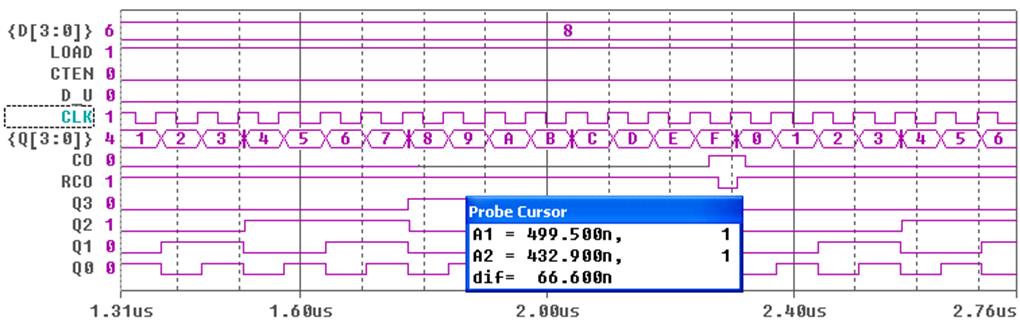

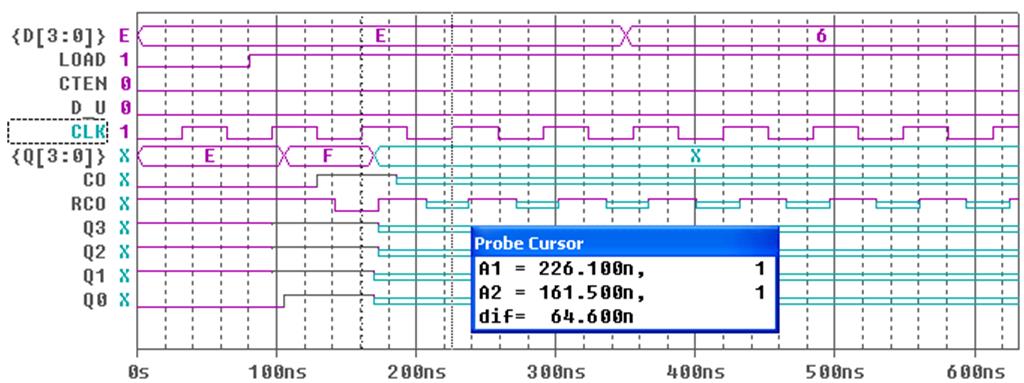

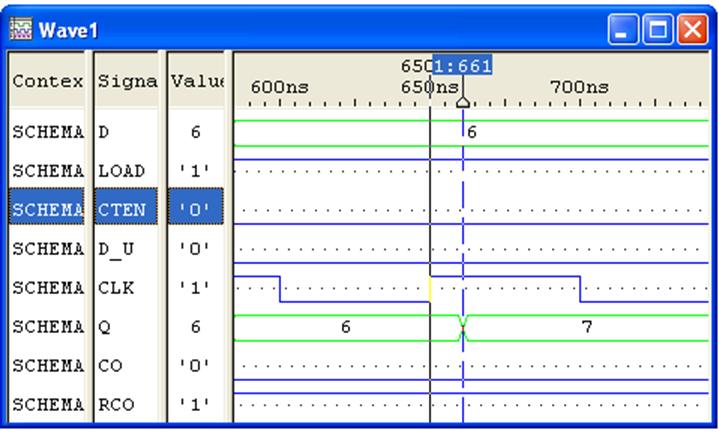

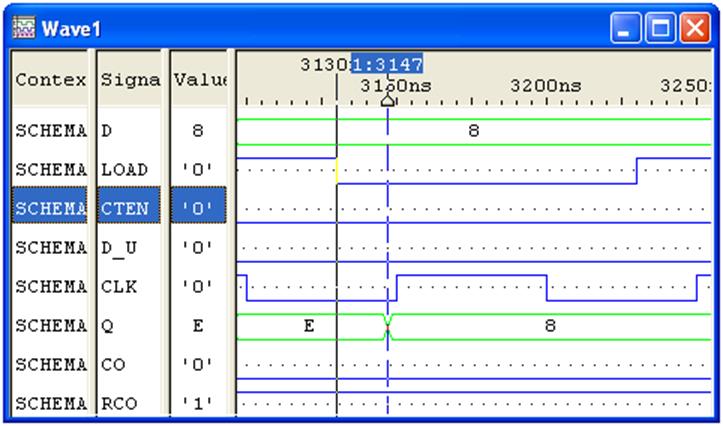

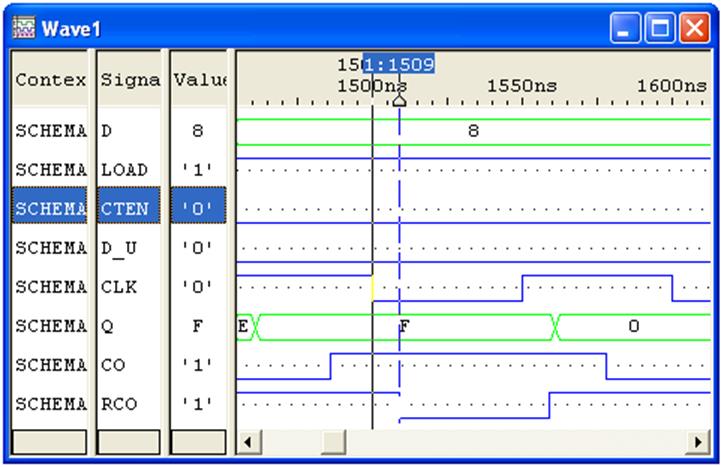

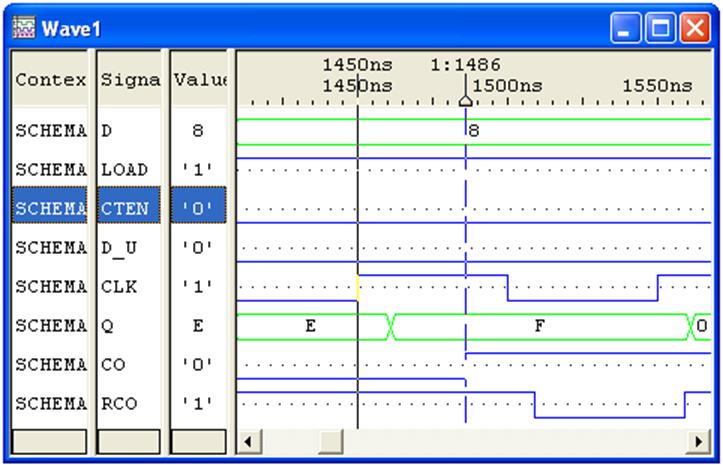

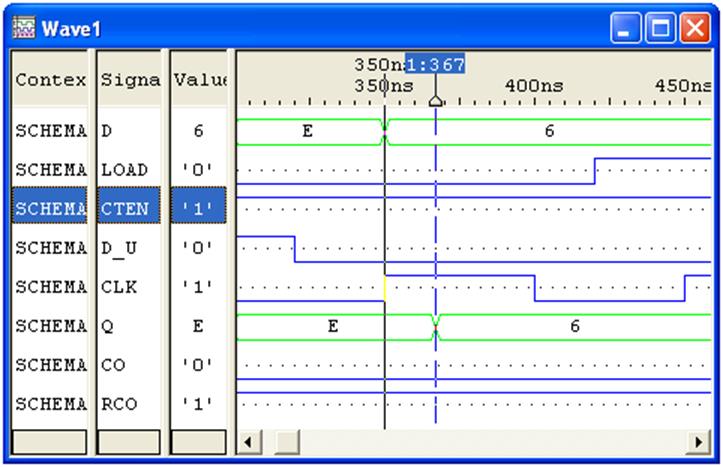

Измеренные задержки распространения сигналов в различных режимах работы счетчика приведены ниже.

Рис.8.1. Задержка распространения сигнала от входов D[3..0] до выходов Q[3..0]

Рис.8.2. Задержка распространения сигнала от входа LOAD до выходов Q[3..0]

Рис.8.3. Задержка распространения сигнала от входа CLK до выходов Q[3..0]

Рис.8.4. Задержка распространения сигнала от входа CLK до выхода RCO

Рис.8.5. Задержка распространения сигнала от входа CLK до выхода CO

Рис.8.6. Задержка распространения сигнала от входа CTEN до выхода RCO

Рис.8.7. Задержка распространения сигнала от входа D_U до выхода CO

Рис.8.8.

Задержка распространения сигнала от входа D_U до выхода RCO

Рис.8.8.

Задержка распространения сигнала от входа D_U до выхода RCO

Как видно на приведенных ниже рисунках, разработанная схема успешно моделируется при тактовой частоте ниже 15 МГц.

Рис.9.1. Нормальная работа счетчика при тактовой частоте равной 15 МГц

Рис.9.2. Сбои функционирования счетчика при тактовой частоте равной 15,5 МГц

9. OrCAD 9.1. PCB Simulate – проект.

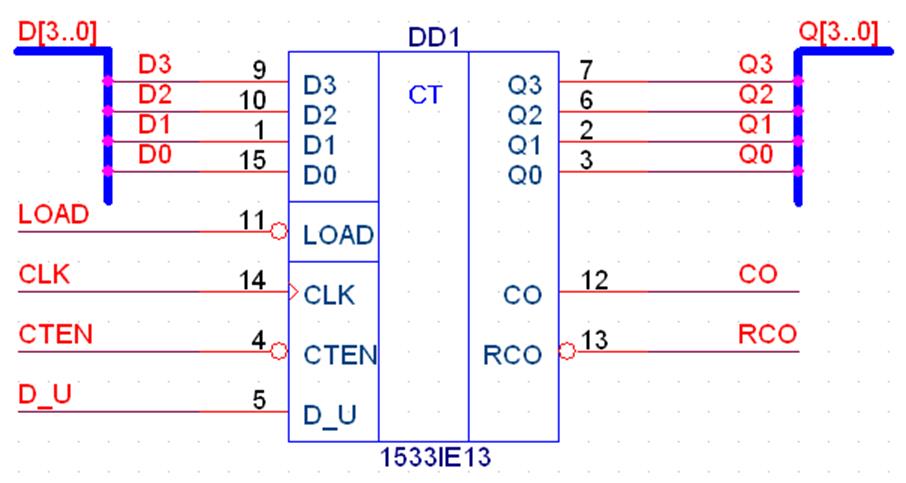

Рис.10. Схема верификации проектируемого узла

Рис.11. Схема замещения проектируемого узла

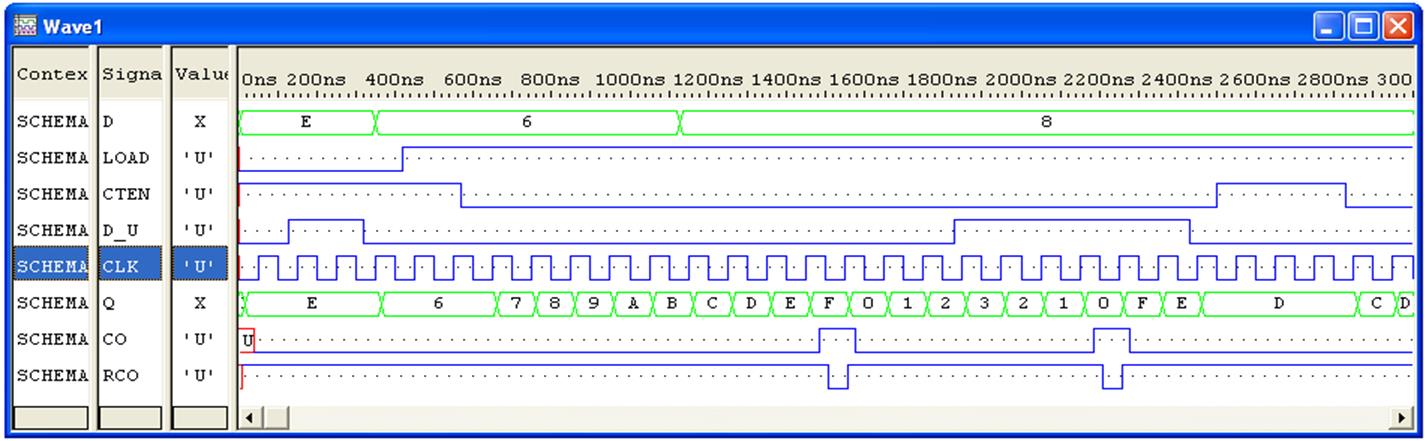

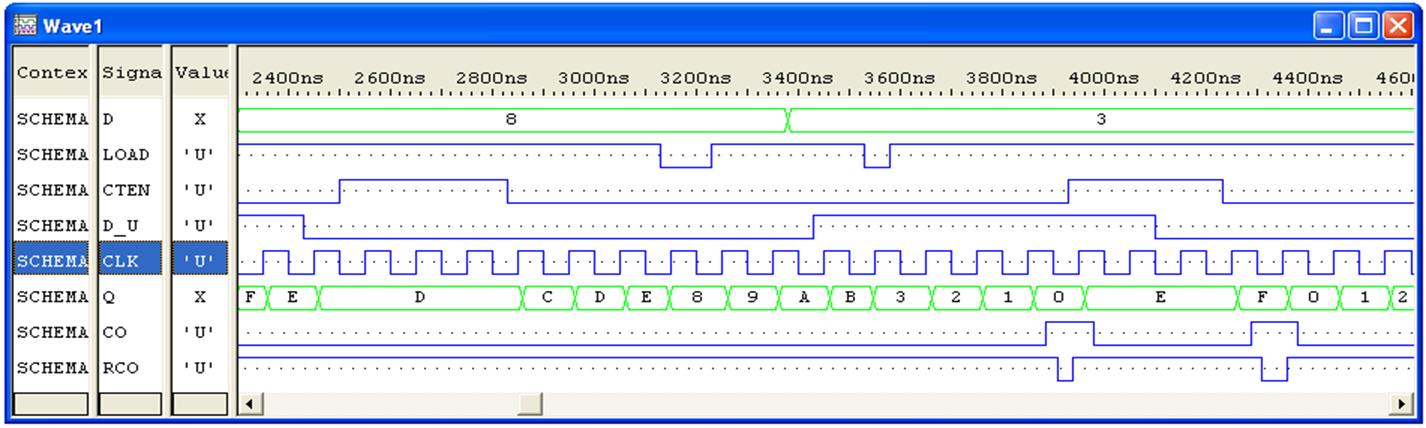

12.1, 12.2, Временные диаграммы, полученные при моделирования схемы, представленной на рис.10 (начало, продолжение)

Рис.13.1. Задержка распространения сигнала от входа CLK до выходов Q[3..0] (11 ns)

Рис.13.2. Задержка распространения сигнала от входа LOAD до выходов Q[3..0] (17 ns)

Рис.13.3. Задержка распространения сигнала от входа CLK до выхода RCO (9 ns)

Рис.13.4. Задержка распространения сигнала от входа CLK до выхода CO (36 ns)

Рис.13.5. Задержка распространения сигнала от входов D[3..0] до выходов Q[3..0] (17 ns)

Анализ результатов моделирования SPICE и PCD Simulate проектов позволяет сделать вывод о принципиальной идентичности функционирования схемы счетчика в заданных режимах.

Вместе с тем существует ряд отличий в результатах моделирования, а именно:

· в ходе реализации PCD Simulate проекта отсутствовали проблемы связанные с выбором типа триггера (в отличии от SPICE проекта см. п.8.3). Схема устойчиво функционирует с любой комбинацией используемых триггеров (в отчете приведена схема замещения с использованием JK триггера 1533ТВ15, а при разработке проекта проверялась работа схемы, как с использованием D триггера 1533ТМ2, так и комбинации этих триггеров);

· незначительно (в пределах 10%) различаются задержки распространения сигналов;

· схема в PCD Simulate проекте нормально функционирует при максимальной частоте сигнала CLK равной 16,5 МГц, а в SPICE проекте на частоте 15 МГц;

· на выходе СО не появляются помехи при моделирования в PCD Simulate проекте в отличие от SPICE проекта.

10. Поведенческая VHDL-модель узла.

library IEEE; --Подключение необходимых библиотек

use IEEE.STD_LOGIC_1164.all;

use IEEE.std_logic_unsigned.all;

entity \IE13_FUNC\ is --Описание объекта;

port(

CLK, LOAD : in STD_LOGIC; --Входы: тактирующий, загрузки,

CTEN, D_U : in STD_LOGIC; --разрешениЯ и направлениЯ счета

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.