Стоит обратить внимание на то, что в комментариях буква “Я” всегда заглавная. Это связано с ещё одной «неожиданной находкой» в САПР OrCAD. Дело в том, что при использовании строчной буквы «я» возникает ошибка: «illegal, non-printing character encountered in input» (вводится непечатаемый символ), не позволяющая произвести компиляцию файла.

11. Схема верификации символа с подключенной к нему VHDL-моделью.

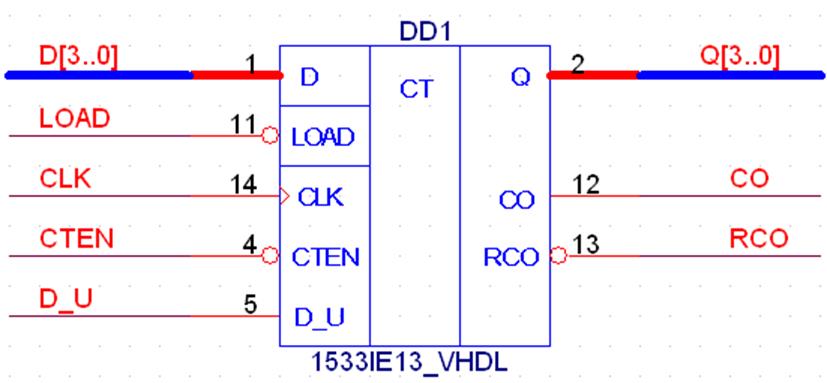

Рис.14. Схема верификации символа с подключенной к нему VHDL-моделью

Для удобства сигналы, поступающие на информационные входы, объединены в шину D[3..0], а выходные сигналы – в шину Q[3..0].

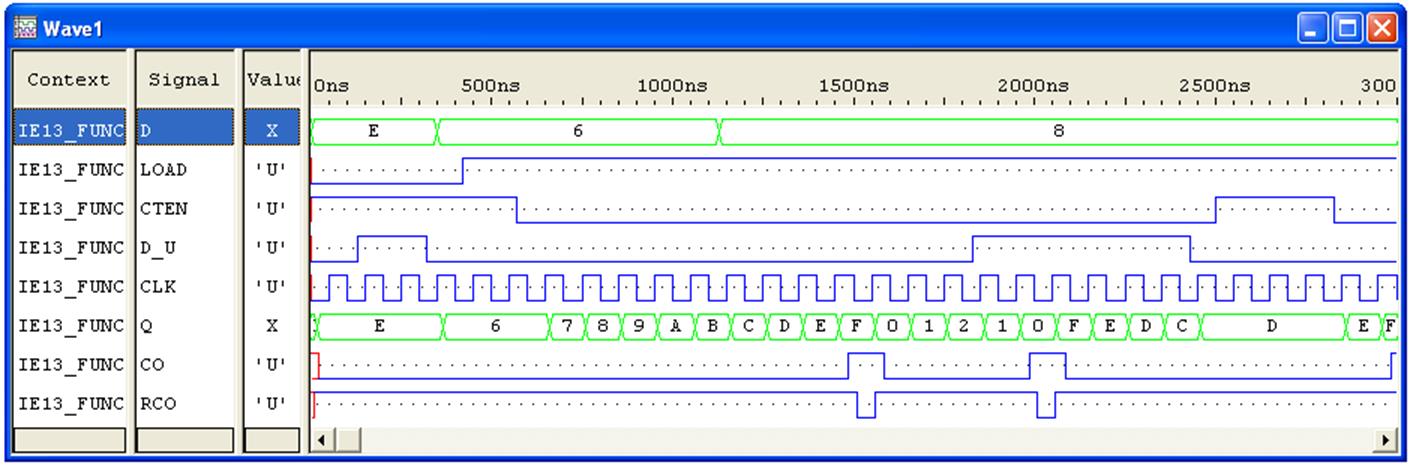

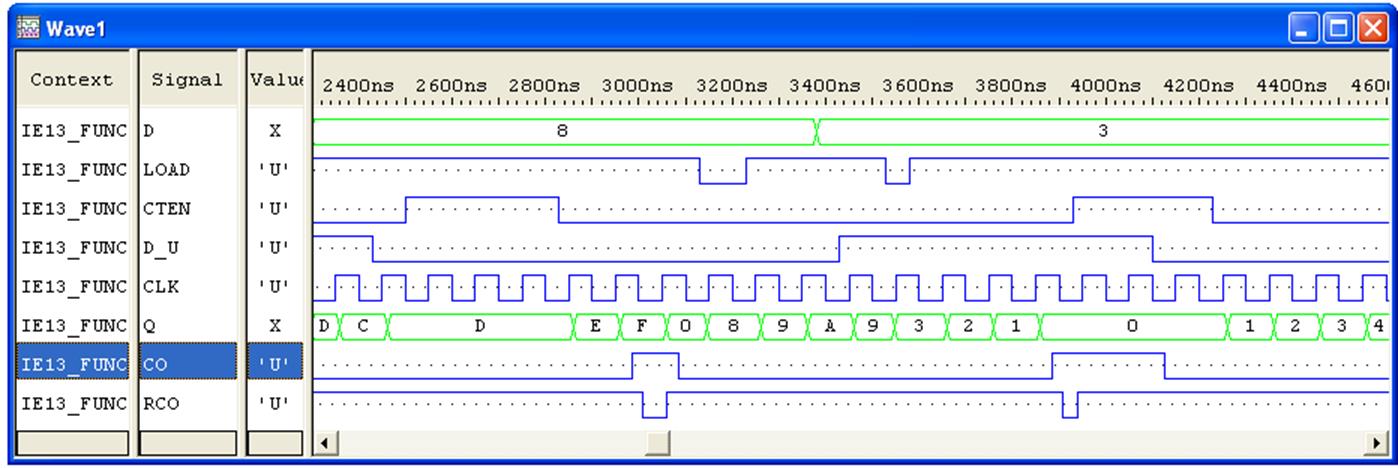

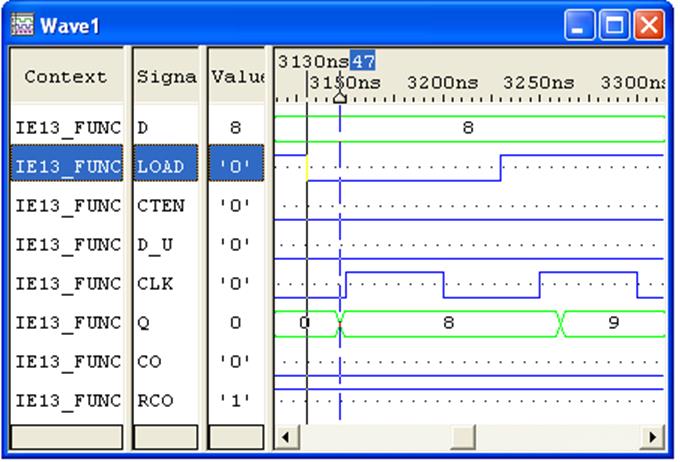

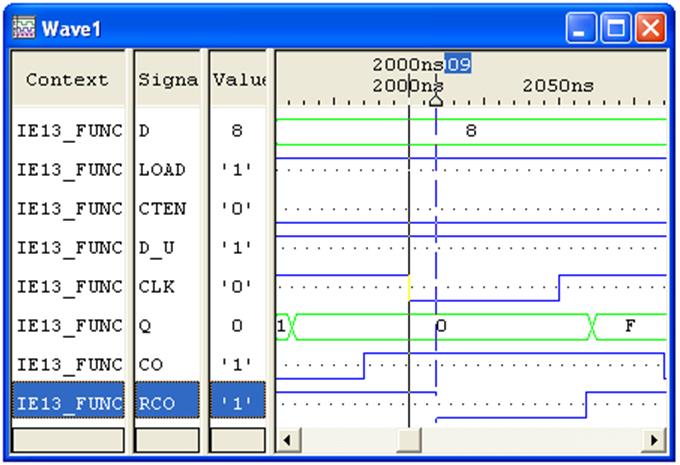

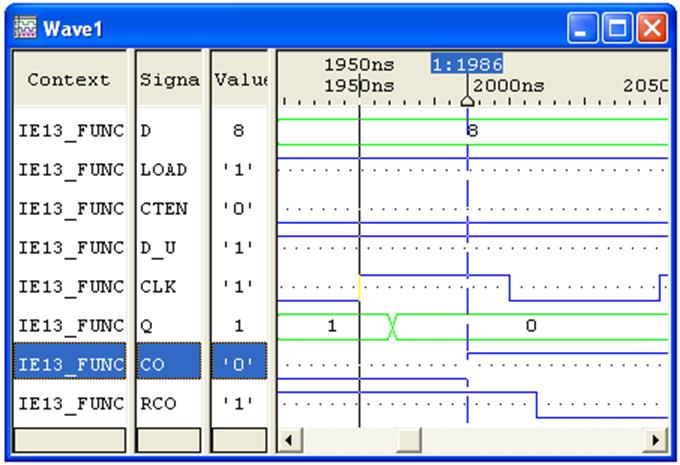

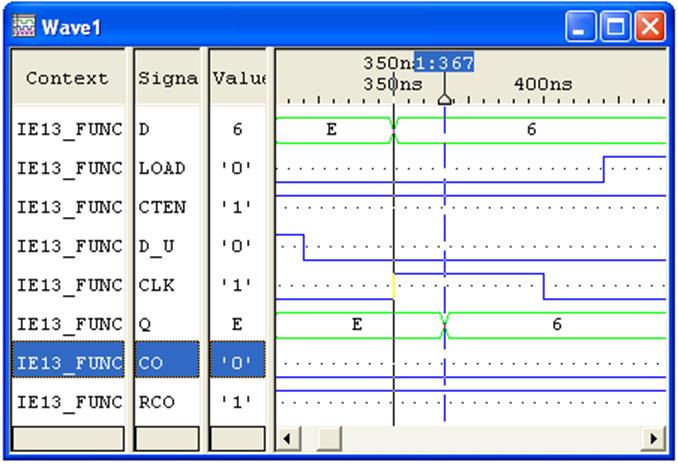

15.1, 15.2, Временные диаграммы, полученные при моделирования схемы, представленной на рис.14 (начало, продолжение)

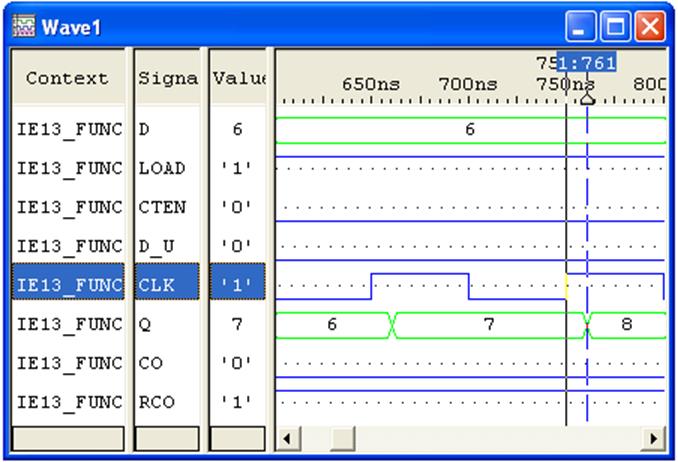

Рис.16.1. Задержка распространения сигнала от входа CLK до выходов Q[3..0] (11 ns)

Рис.16.2. Задержка распространения сигнала от входа LOAD до выходов Q[3..0] (17 ns)

Рис.16.3. Задержка распространения сигнала от входа CLK до выхода RCO (9 ns)

Рис.16.4. Задержка распространения сигнала от входа CLK до выхода CO (36 ns)

Рис.16.5. Задержка распространения сигнала от входов D[3..0] до выходов Q[3..0] (17 ns)

Величины задержек, измеренные при моделировании VHDL-модели, соответствуют значениям, измеренным в пункте 9.3.

Результат контроля временных соотношений:

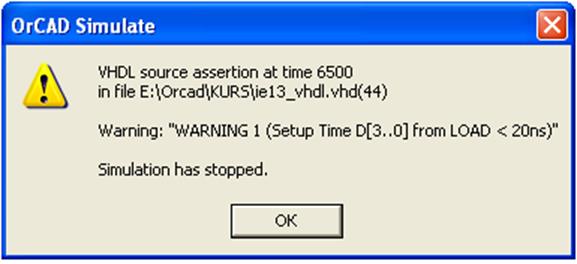

При несоблюдении ограничения на время предустановки данных процесс моделирования приостанавливается. На экране отображается сообщение (Рис. 14).

Рис.17. Сообщение об ошибке

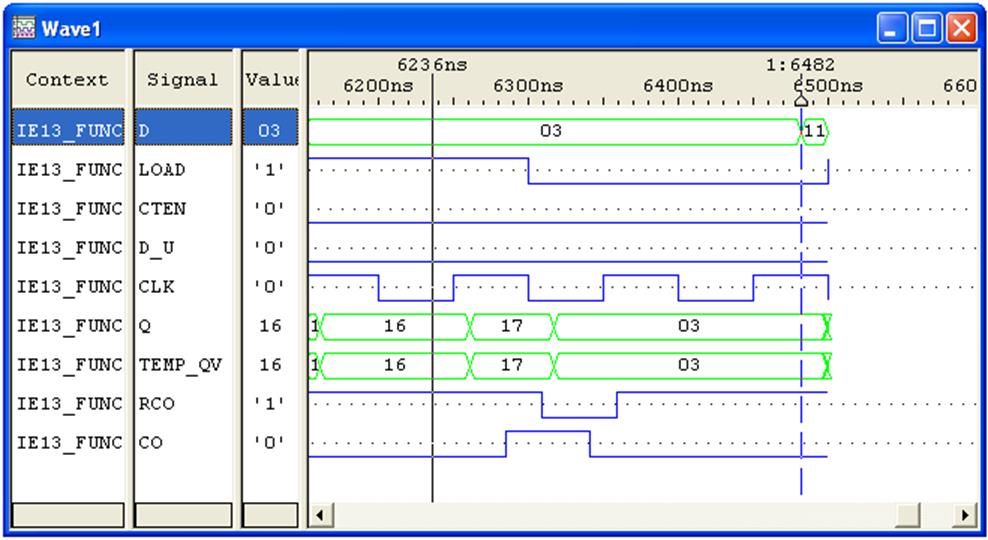

Временная диаграмма в данный момент выглядит следующим образом (Рис.18)

Рис.18. Временная диаграмма, образованная до обнаружения ошибки во временном соотношении.

Как видно, переключение сигнала LOAD в ‘1’ происходит через 18 ns после переключения на шине D. Это значение меньше времени предустановки данных, равном 20 ns.

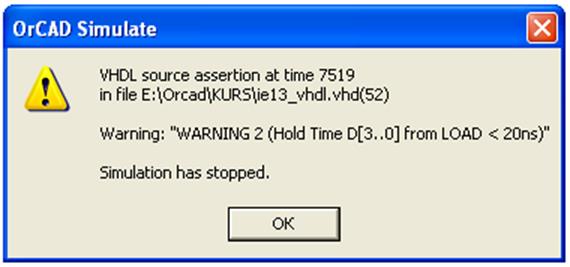

При несоблюдении ограничения на время удержания данных процесс моделирования также приостанавливается. На экране отображается сообщение (Рис. 19).

Рис.19. Сообщение об ошибке

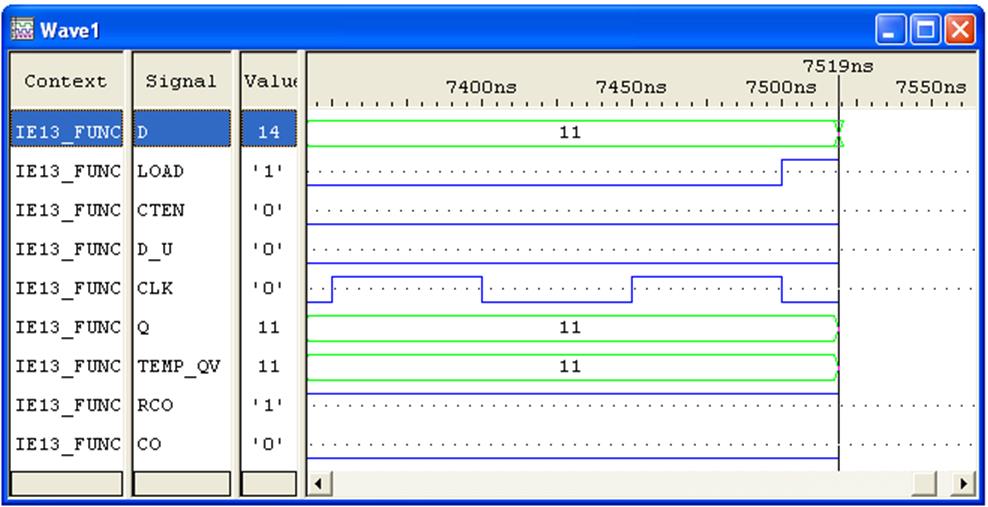

Временная диаграмма (рис.20)

Рис.20. Временная диаграмма, образованная до обнаружения ошибки во временном соотношении.

Переключение сигнала на шине D происходит через 19 ns после переключения LOAD. Это значение меньше времени удержания данных, равном 20 ns.

12. Active– HDL 8.1.

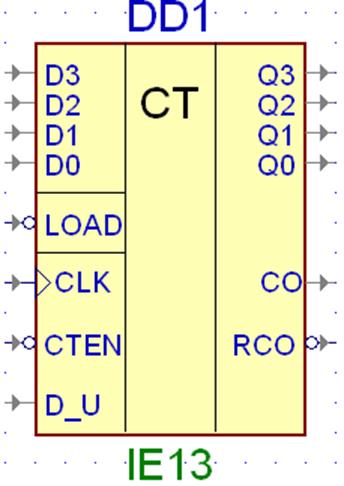

Рис.21. УГО разрабатываемого счётчика, выполненное в пакете Active - HDL 8.1

Рис.22. Схема замещения проектируемого узла

13. Поведенческая модель на языке VHDL.

library IEEE;

use IEEE.STD_LOGIC_1164.all; --Подключение необходимых библиотек

use IEEE.std_logic_unsigned.all;

entity VHD_block is

port( --Перечень входных и выходных портов

D3 : in STD_LOGIC; --Информационные входы

D2 : in STD_LOGIC;

D1 : in STD_LOGIC;

D0 : in STD_LOGIC;

LOAD : in STD_LOGIC; --вход загрузки

CLK : in STD_LOGIC; --тактирующий вход

CTEN : in STD_LOGIC; --вход разрешения счета

D_U : in STD_LOGIC; --вход выбора направления счета

Q3 : out STD_LOGIC; --Выходы разрядов счетчика

Q2 : out STD_LOGIC;

Q1 : out STD_LOGIC;

Q0 : out STD_LOGIC;

RCO : out STD_LOGIC; --Выход наращивания счета

CO : out STD_LOGIC --Выход переноса

);

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.