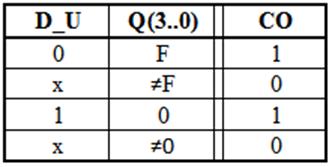

Таблица 2.2. Таблица 2.3.

6. Таблица реальных задержек.

Данные, приведенные ниже, взяты из источников [1], [5].

|

Обозна-чение |

Вход |

Выход |

Величина максимальной задержки, нс |

|

tPLH |

LOAD |

Q[3..0] |

30 |

|

tPHL |

30 |

||

|

tPLH |

D[3..0] |

Q[3..0] |

21 |

|

tPHL |

21 |

||

|

tPLH |

CLK |

RCO |

20 |

|

tPHL |

20 |

||

|

tPLH |

CLK |

Q[3..0] |

18 |

|

tPHL |

18 |

||

|

tPLH |

CLK |

CO |

31 |

|

tPHL |

31 |

||

|

tPLH |

D_U |

RCO |

37 |

|

tPHL |

28 |

||

|

tPLH |

D_U |

CO |

25 |

|

tPHL |

25 |

||

|

tPLH |

CTEN |

RCO |

18 |

|

tPHL |

18 |

Таблица 3. Задержки переключений на выходах счётчика при переключениях сигнала на входах из низкого уровня напряжения в высокий (tPLH) и из высокого уровня в низкий (tPHL).

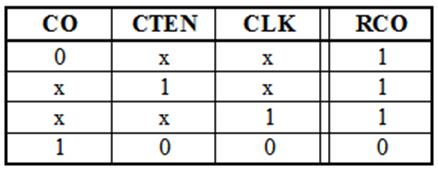

Требования к временным соотношениям в схеме:

Время предустановки данных: tsu ≥ 20 ns;

Время удержания данных:

- после загрузки данных с информационных входов (снятие сигнала LOAD) th ≥ 20 ns;

- в остальных случаях th ≥ 0 ns;

Рис.2. Время предустановки (tsu) и время удержания (th) данных

7. Описание работы проектируемого узла

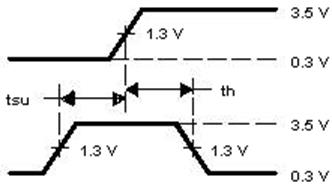

Микросхема KP1533ИЕ13 представляет собой четырёхразрядный синхронный двоичный реверсивный счётчик с параллельной загрузкой [1].

При низком уровне напряжения на входе разрешения счета (CTEN) переключение триггеров счетчика происходит по фронту синхроимпульса на входе CLK. Высокой уровень напряжения на входе CTEN запрещает счет и на выходе счетчика сохраняется предыдущее состояние.

Прямой счет осуществляется при низком уровне напряжения на входе D_U, обратный счет - при высоком уровне на этом входе.

Асинхронная установка счетчика в заданное по входам D0, D1, D2, D3 состояние осуществляется подачей низкого уровня напряжения на вход LOAD.

В микросхеме предусмотрены выходы для каскадного соединения счетчиков. На выходе CO устанавливается напряжение высокого уровня при достижении значения кода на выходе счетчика равного “пятнадцати” (1111) для прямого счета и “нуля” - для обратного.

Для установки низкого уровня напряжения на выходе RCO необходимо наличие высокого уровня сигнала на выходе CO и низкого уровня на входе CLK.

8. OrCAD 9.1. SPICE – проект.

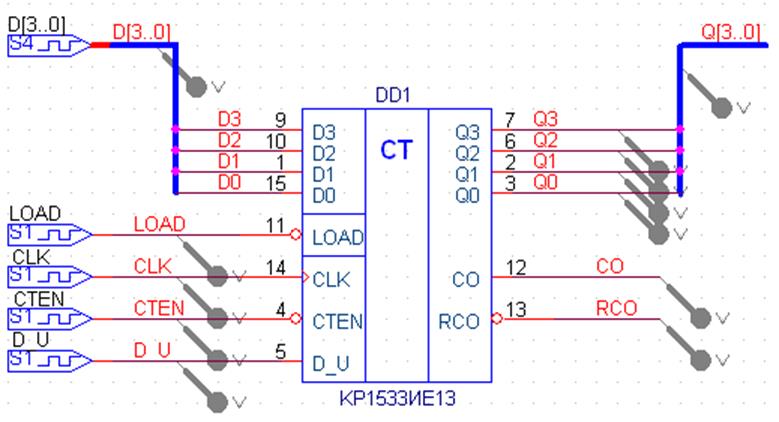

Рис.3. УГО разрабатываемого счётчика, выполненное в пакете OrCAD 9.1

Рис.4. Схема замещения иерархического символа

Рис.5. Схема верификации иерархического символа

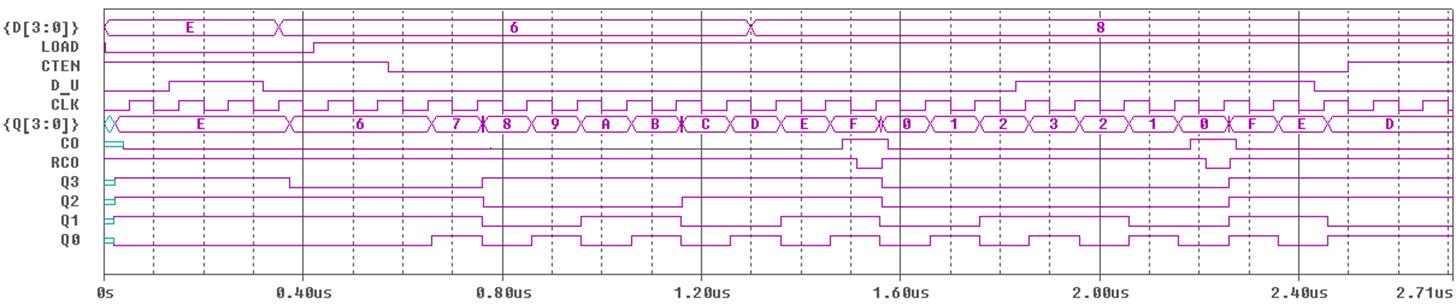

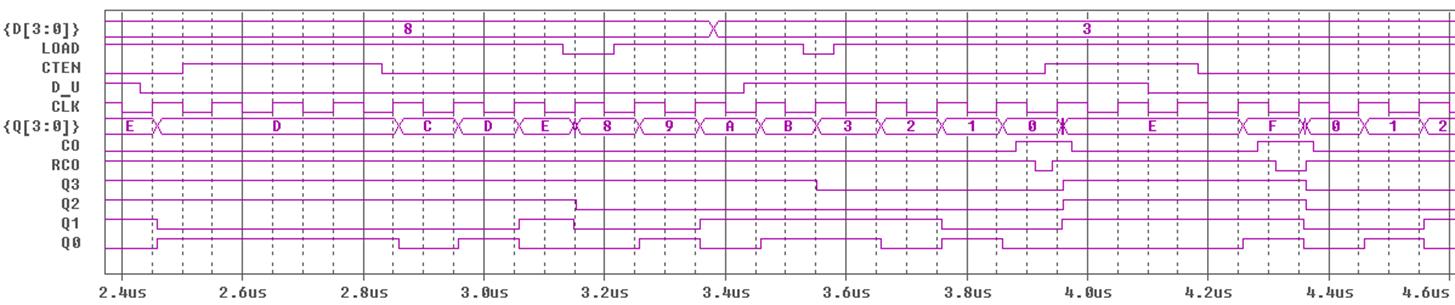

Результаты моделирования схемы, представленной на рис.5.

![]()

![]()

![]()

![]()

Рис.6.1, 6.2. Временные диаграммы, полученные при моделирования схемы, представленной на рис.5.

Как видно на рис. 6.1, 6.2, разработанная схема нормально функционирует в заданных режимах. Следует обратить внимание на то, что в схеме пришлось использовать два типа триггера - D триггер 1533ТМ2 и JK триггер 1533ТВ15, подключенный по схеме D триггера. Это вызвано тем, что, несмотря на равнозначность с точки зрения схемотехники (с учетом схем включения) этих триггеров, программа моделирования выдает ошибку (Х – состояние) при использовании во всех разрядах триггеров одного типа. Данный эффект возникает в процессе моделирования в случаи появления на D входе триггера «естественной» помехи, формируемой на комбинационной части схемы в результате изменения выходного кода счетчика. И, несмотря на то, что данная помеха пропадает задолго до прихода очередного фронта сигнала CLK, программа отказывается корректно моделировать схему.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.