SRAM – (512К*32)

Flash File – (128*32)

При реализации основной памяти ЭВМ будем исходить из следующих предпочтений:

· Минимальные схемные затраты

· Минимальное число физических страниц – как следствие максимально простое управление памятью.

В качестве элементной базы памяти были выбраны следующие МС:

SRAM – IDT71V424.

Ее основные характеристики:

· Напряжение питания – 3.3V

· Информационная организация – (512К*8)бит.

· Время доступа к памяти – 15нс.

· Время выборки адреса – 15нс.

Flash File – Am29F0I0B.

Ее основные характеристики:

· Напряжение питания – 5V

· Информационная организация – (128К*8)бит.

· Время доступа к памяти – 45нс.

· Время выборки адреса – 45нс.

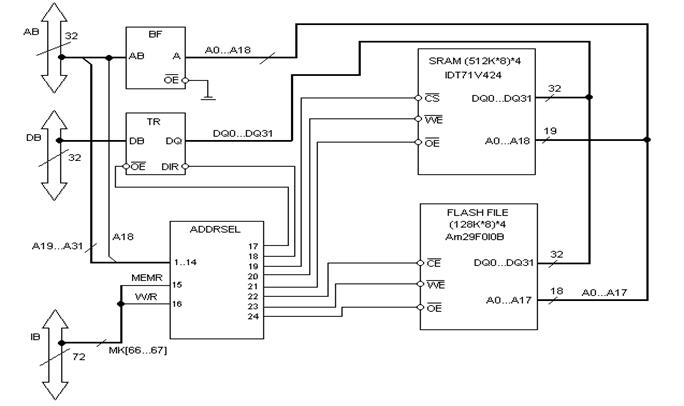

Учитывая информационную организацию требуемой памяти и выбранных типономиналов микросхем, делаем вывод, что требуется 8 МС для организации модуля основной памяти ЭВМ (4 – SRAM, 4 – Flash File). Ниже на рис. 6.1 представлена карта памяти спроектированного модуля. На рис. 6.2 представлена функциональная схема самого модуля.

|

Рис. 6.1 Карта памяти

На функциональной схеме модуля памяти блоки SRAM и FLASH памяти представлены каждый в виде одного «черного ящика». Каждый из этих блоков состоит из 4 МС памяти. Наращивание проведено для достижения необходимой разрядности слова (32 бита). При этом адресные линии разведены параллельно. Линии данных положены рядом.

Рис. 6.2 Функциональная схема модуля памяти

При проектировании модуля памяти была использована следующая дополнительная элементная база:

Буфер – CY74FCT16244T (использовано 2 устройства)

Трансивер - CY74FCT16245T (использовано 2 устройства)

Адресный селектор – CPLD - ATF1502ASL

|

Номер вывода |

Функциональное назначение |

|

1…14 |

Бита адреса подлежащие проверке |

|

15 |

70-й бит МК (разрешение работы памяти) |

|

16 |

71-й бит МК (выбор запись/чтение) |

|

17 |

Разрешение работы трансивера |

|

18 |

Выбор направления передачи данных трансивером |

|

19 |

Выбор кристалла SRAM |

|

20 |

Разрешение записи SRAM |

|

21 |

Разрешение вывода SRAM |

|

22 |

Выбор кристалла FLASH FILE |

|

23 |

Разрешение записи FLASH FILE |

|

24 |

Разрешение вывода FLASH FILE |

Адресный селектор функционирует по следующей логике: если среди битов А19…31 есть хоть одна единица, то данный адрес предназначен не для данной памяти, при этом формируется бит прерывания (лог. «1») и бит подтверждения прерывания (лог «0»). Этот бит приостанавливает работу секвенсора, т.к. больше памяти у данной ЭВМ нет, а обращение по неверному адресу является ошибкой. Процессор данной ЭВМ способен генерировать 32 бита адреса, т.е. разработанная память может быть расширена, но изменение существующей конфигурации памяти ЭВМ повлечет за собой необходимость перестройки селектора.

Ниже в таблице 7.1 представлен формат микрокоманд. Микрокоманды «зашиваются» в МПП.

Таблица 7.1. Формат микрокоманд

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.