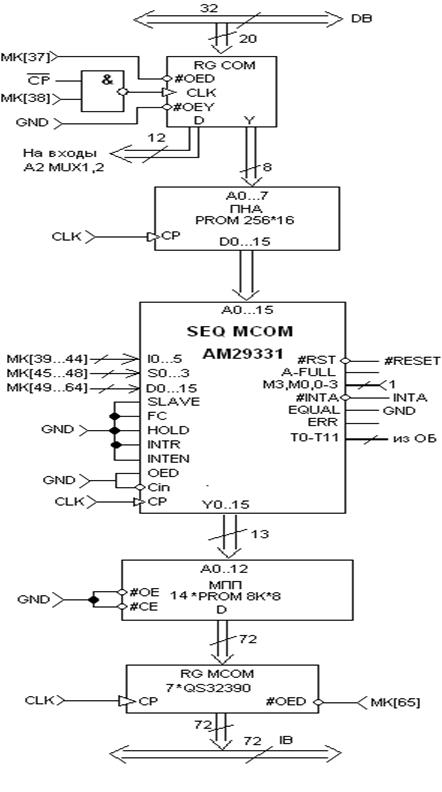

МУУ представляет собой конвейер, функциональное назначение которого – получив команду из основной памяти потактово выдавать микрокоманды на шину управления, которые входят в данную команду. Разработанная структура МУУ является классической. МУУ включает в себя: регистр команд, преобразователь начального адреса (здесь и далее ПНА), секвенсор микрокоманд, микропрограммную память (здесь и далее МПП), регистр микрокоманд. Ниже на рис. 5.1 представлена функциональная схема МУУ. В качестве регистра команд используется два регистра FCT16374T (16-разрядный регистр). Выходной порт одного из регистров используется для передачи данных в ПНА, выходной порт второго регистра используется для передачи адресов РОН в ОБ (входы А2 мультиплексоров 1,2 – см. рис. 4.1).

Секвенсор микрокоманд АМ29331 поддерживает прерывания реального времени на макро - и микроуровнях управления со временем реакции, не превышающем длительность микроцикла (80-90нс). Обладает встроенной логикой тестирования входных условий, а также встроенной логикой обнаружения контрольной точки в микрокоде для отладки микропрограмм и накопления статистики. Обеспечивает контроль ошибок в режиме “ведущий-ведомый”. В разработанном МУУ используется лишь часть функциональных возможностей секвенсора. Соответственно, те входы и выходы секвенсора, которые ответственны за выполнение ненужных функций, не используются. На входы поданы постоянные логические уровни, которые пассивизируют данные входы. Выходы A-FULL и ERR оставлены свободными.

Рис. 5.1 Функциональная схема микропрограммного устройства управления

Для организации регистра команд было использовано два регистра QS32390 – для организации двух портов ввода/вывода (один для кода операции, другой для адреса операндов, хранящихся в РОН). Разрядность слова МПП выполнена в соответствии с форматом микрокоманд (Таблица 7.1). МПП выполняется в виде энергонезависимой памяти. Согласно индивидуальному варианту задания МПП должна иметь средства контроля паритета. Цель контроля паритета – отслеживать правильность выдачи данных из памяти. Помимо основных ячеек устройство памяти имеет дополнительно один бит памяти на каждое хранимое слово. При «прошивке» МПП записываемые слова сворачиваются по модулю 2 и сохраняются в виде дополнительного паритетного бита. При чтении данные сворачиваются еще раз и производится сравнение бита новой свертки и бита, сохраненного при записи. Если паритетные биты совпали, данные выдаются на шину, если нет, то формируется сигнал ошибки, который прерывает операцию чтения. Контроль паритета можно не использовать, если МПП имеет очень высокую надежность хранения данных. Подходящей является МС CY7C265. Данная микросхема является синхронной PROM, синхронный режим мы не используем, данная микросхема имеет возможность работы в асинхронном режиме. В качестве ПНА использована МС CY7C225A.

Приведем основные характеристики данной МС:

· Напряжение питания – 5В.

· Время доступа – 25нс.

Расчет времени цикла будем проводить, просматривая пути прохождения сигналов, которые могут оказаться критическими.

Рассмотрим путь №1:

Выборка следующей микрокоманды: время доступа к МПП + время предустановки регистра микрокоманд = 15 + 5,2 = 20,2нс.

Рассмотрим путь №2:

Начало новой команды: время предустановки ПНА + время задержки выдачи данных ПНА + задержка от входа А0-15 до Y0-15. = 18+12+25 = 55нс.

Поскольку при расчете минимального времени цикла ОБ были получены значения превосходящие значения для МУУ (79,7нс.).

Основой разработки основной памяти ЭВМ будет являться расчетно-графическая работа по дисциплине «Схемотехника» - «Проектирование модуля памяти». Согласно индивидуальному варианту основная память микроЭВМ должна включать SRAM и Flash File память объемом 2М и 512К соответственно. Разрядность соответствует разрядности генерируемых процессором слов данных и адреса, т.е. 32 разряда. Вычислим информационную организацию проектируемого модуля памяти.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.