OUTA0-OUTA3 выходы:

Выходные сигналы, посылающие данные на сегменты дисплея (старшие е—g, dp).

OUTB0-OUTB3 выходы:

Выходные сигналы, посылающие данные на сегменты дисплея (младшие a—d).

~RD вход:

Входной вывод ~RD (read — чтение) напрямую соединяется с сигналом ~IORC или ~RD микропроцессорной системы. Соответствующий сигнал на этом выводе осуществляет чтение из информационных регистров или регистров состояния, когда сигнал на выводе ~CS имеет низкий логический уровень.

RESET вход:

Вывод RESET (сброс) соединяется с одноименным сигналом системы и предназначен для выполнения сброса регистров устройства.

RL7-RL0 входы:

Входные выводы RL7—RLO (return line — обратная линия) используются для восприятия любого нажатия клавиши в матрице клавиатуры при ее сканировании.

SHIFT вход:

Входной вывод SHIFT (смена регистра) обычно соединяется с одноименной клавишей <Shift> на клавиатуре.

SL3-SL0 выходы:

Выходные сигналы на выводах SL3—SLO (scan line — линия сканирования) предназначены для сканирования матрицы клавиатуры или цифрового индикаторного табло (дисплея).

~WR вход:

Входной вывод WR (write — запись) присоединяется к любому сигналу строба записи, формируемого внешней логикой. Сигнал низкого уровня на выводе ~WR позволяет производить запись данных в любой информационный или управляющий регистр интерфейса 8279.

Vcc вход:

Вывод "питание" соединяется к источнику постоянного тока напряжением +5,0 В.

Vss вход:

Вывод "земля" присоединяется к выводу "земля" источника питания.

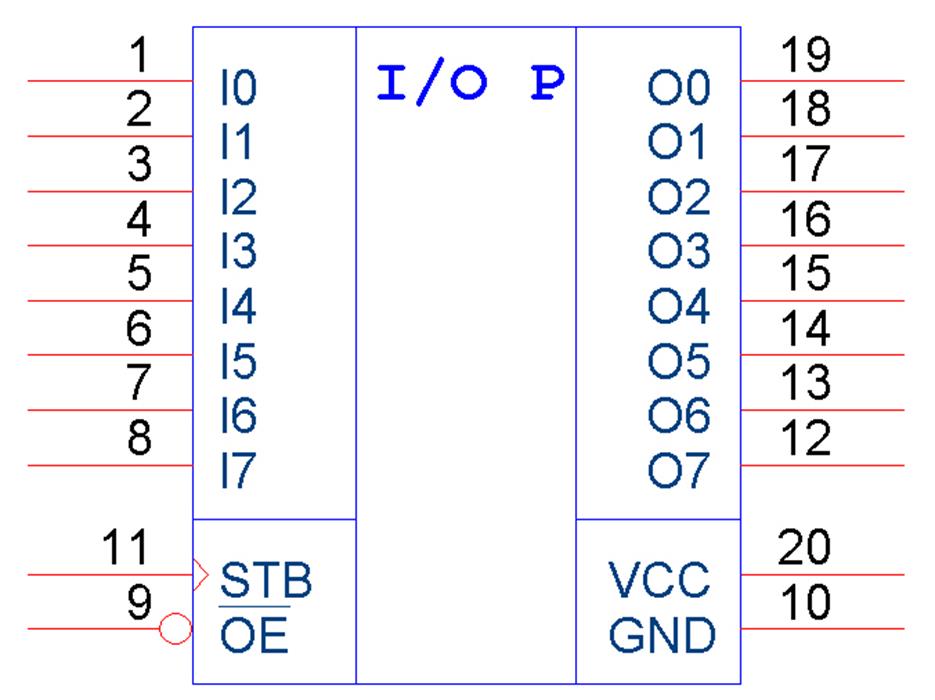

Восьми разрядный регистр защелка с прямыми выходами (без инверсии). Можно использовать как буфер.

Рисунок 5 – УГО I-8282.

Назначение выводов I-8282:

STB вход:

Строб. Когда STB активен (STB = 1), 8282 – прозрачен. Изменение STB с единицы до нуля защелкивает данные.

~OE вход:

Разрешение выхода. Активный уровень – низкий. Когда активен, на выходы O7-O0 выдается содержимое регистра. Когда пассивен, O7-O0 принимают Z состояние.

I7-I0 входы:

Шина входных данных.

O7-O0 выходы:

Шина выходных данных.

Vcc вход:

Вывод "питание" соединяется к источнику постоянного тока напряжением +5,0 В.

GND вход:

Вывод "земля" присоединяется к выводу "земля" источника питания.

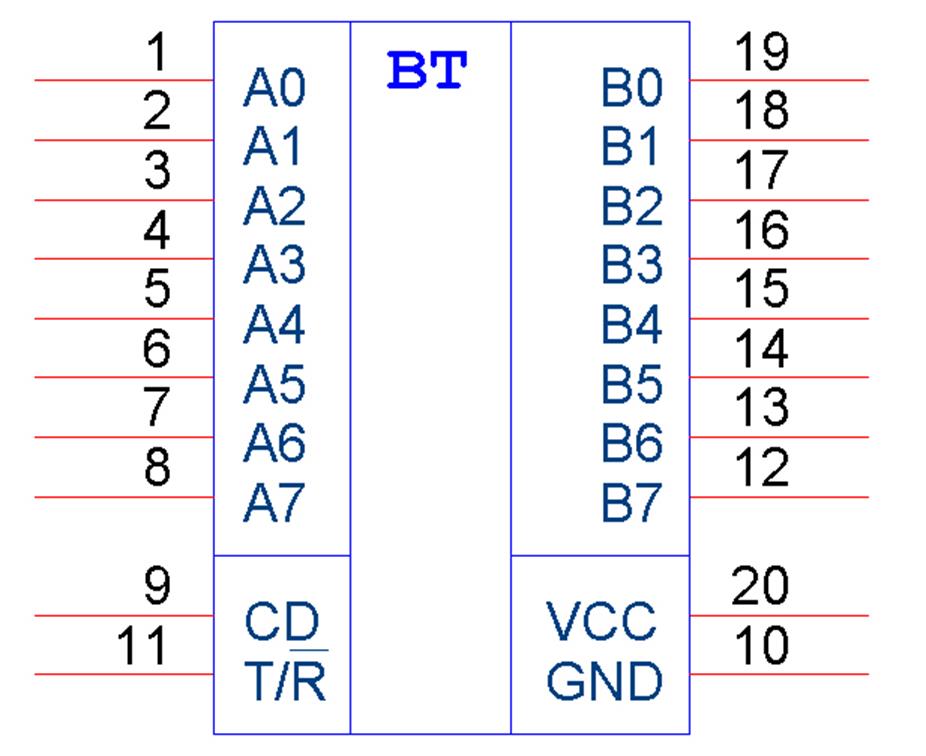

Двунаправленный восьмиразрядный шинный формирователь.

Рисунок 6 – УГО I-8286.

Назначение выводов I-8286:

A7-A0 входы/выходы:

Входы, когда T/~R имеет уровень логической единицы и выходы, когда имеет уровень логического нуля.

B7-B0 входы/выходы:

Входы, когда T/~R имеет уровень логического нуля и выходы, когда имеет уровень логической единицы.

D/~T вход:

Сигнал на этом выводе определяет направление передачи. Высокий уровень – передача от A к B. Низкий уровень – передача от B к A.

CD вход:

CD (chip disable) переводит все выводы в 3е состояние, когда имеет высокий уровень. По сути, то же самое, что ~CS.

Vcc вход:

Вывод "питание" соединяется к источнику постоянного тока напряжением +5,0 В.

GND вход:

Вывод "земля" присоединяется к выводу "земля" источника питания.

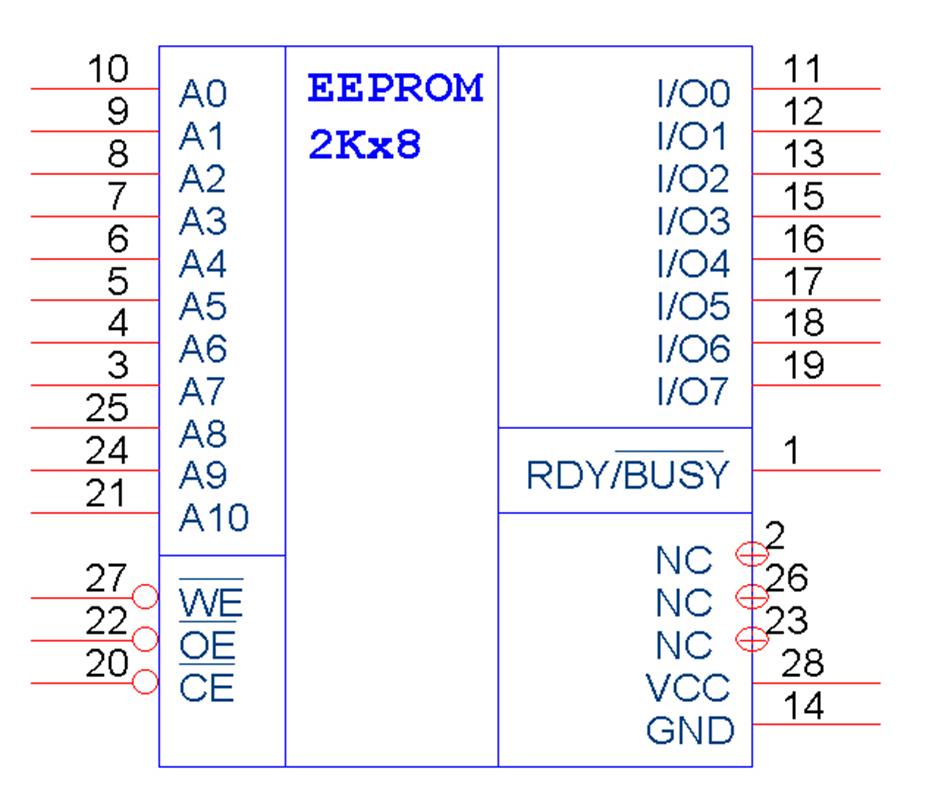

Электрически стираемое перепрограммируемое постоянное запоминающее устройство объемом 2кб с внутренней организацией 2Kx8. Выполнено по КМОП технологии.

Рисунок 7 – УГО AT28C17.

Назначение выводов AT28C17:

A0-A10 входы:

Адресные входы.

~OE вход:

Разрешение выхода. Активный уровень – низкий. Когда пассивен, IO7-IO0 принимают Z состояние.

~СE вход:

Chip enable – включение кристалла. Низкий уровень на этом выводе позволяет работать с памятью.

IO7-IO0 входы/выходы:

Двунаправленная шина данных.

~WE вход:

Разрешение записи. Когда имеет уровень логического нуля, позволяет писать в память.

RDY/~BUSY выход:

Флаг окончания цикла записи. Выход с открытым коллектором.

Vcc вход:

Вывод "питание" соединяется к источнику постоянного тока напряжением +5,0 В.

GND вход:

Вывод "земля" присоединяется к выводу "земля" источника питания.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.