Министерство образования и науки Российской Федерации

Федеральное агентство по образованию

Государственное образовательное учреждение

высшего профессионального образования

Новосибирский государственный технический университет

Кафедра ВТ

|

Расчетно-графическое задание

по дисциплине «Микропроцессорные системы»

Группа: АМ-709

Вариант: 10

Студент: Максименко Д.С.

Преподаватель: Дружинин А.И.

Новосибирск, 2011

Аннотация

Настоящая работа проведена с целью изучения построения микропроцессорной системы по заданным техническим требованиям.

Производится постановка задачи, разработка функциональной схемы, разработка принципиальной электрической схемы со спецификацией, описание построенной микропроцессорной системы и фрагмент программы на ассемблере, инициализирующей режимы работы периферийных БИС.

Содержание

1. Задание. 4

2. Описание микросхем.. 5

2.1 I-8088. 5

2.2 I-8284. 10

2.3 I-8255. 14

2.4 I-8279. 16

2.5 I-8282. 20

2.6 I-8286. 21

2.7 AT28C17. 22

2.8 CY7C135. 24

3. Функциональная схема и её описание. 27

4. Принципиальная схема с перечнем элементов и её описание. 29

5. Программирование I-8279. 34

Заключение. 39

Список использованных источников. 40

Приложение А. Функциональная схема МПС.. 41

Приложение Б. Принципиальная электрическая схема МПС.. 42

Приложение В. Спецификация. 45

Разработать микропроцессорную систему на базе микропроцессора I-8088, содержащую:

· RAM – 4 кб;

· ROM –2 кб;

· Периферия – I-8255, I-8279.

16ти разрядный микропроцессор с шиной данных на 8 бит и шиной адреса 20 бит. Является модификацией процессора I-8086, обладающий такой же системой команд, но совместимый с 8-битным оборудованием для процессоров 8080/8085. Использовался как переходное звено от 8080/8085 к 8086. Выполнен по усовершенствованной МОП технологии. Частота тактирования 5 МГц. Имеет два режима работы: минимальный и максимальный. Максимальный режим в данной работе никак не затрагивается.

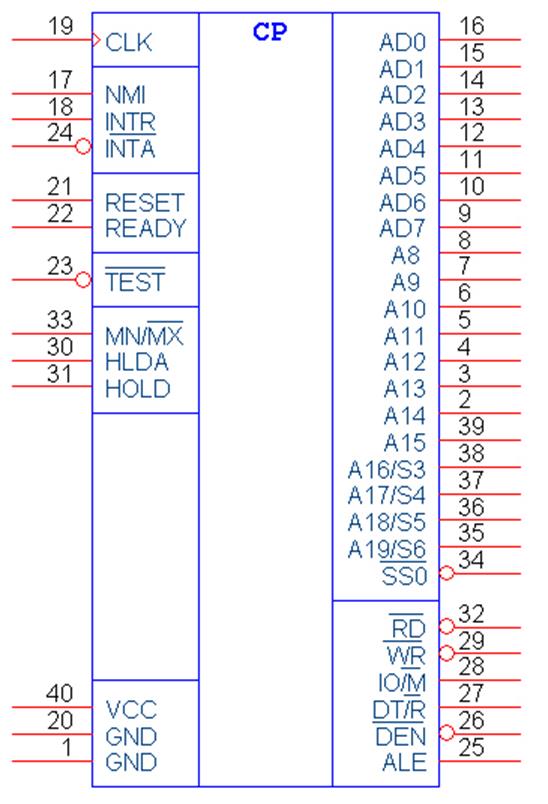

Рисунок 1 – УГО I-8088.

Назначение выводов I-8088:

Общие выводы:

AD7-AD0 выходы/входы:

Линии мультиплексированной шины адреса/данных, содержат младшие 8 битов адреса памяти или порта ввода-вывода при активизации сигнала на выводе процессора ALE, либо 8 битов данных, если сигнал ALE пассивен. При подтверждении фиксации сигналов переходят в Z.

A15-A8выходы:

Адресная шина. Обеспечивает систему памяти старшими адресными битами, которые присутствуют во всех циклах шины. При подтверждении фиксации сигналов переходят в Z.

ADA19/S6-A16/S3 выходы:

Биты адреса/индикации состояния процессора. При подтверждении фиксации сигналов переходят в Z. Бит S6 всегда сохраняет логический ноль, бит S5 показывает состояние бита управления прерываниями IF (interrupt enable flag) регистра флагов, а S4 и S3 обозначают, к какому из сегментов памяти имеется доступ во время текущего цикла шины.

~RD выход:

Каждый раз, когда сигнал считывания на этом выводе активен, т. е. имеет уровень логического 0, информационная шина восприимчива к данным, поступающим из памяти или устройств ввода-вывода, подключенных к системе. Этот вывод переходит в состояние высокого импеданса при подтверждении фиксации сигнала.

READY вход:

Сигналом на этом выводе управляется вставка тактов ожидания в цикл синхронизации микропроцессора. Если сигнал на выводе READY пассивен, т. е. имеет уровень логического нуля, то микропроцессор переходит в состояние ожидания и не занят. Если же сигнал активен, т. е. имеет уровень логической единицы, то это не оказывает никакого действия на выполняемую микропроцессором операцию.

INTR вход:

Сигнал запроса прерывания на выводе INTR (interrupt request) используется для запроса аппаратного прерывания у процессора. Если сигнал активен, т. е. имеет значение логической 1, и при этом установлен бит управления прерыванием регистра флагов (IF = 1), то микропроцессор после завершения исполнения текущей команды переходят в цикл подтверждения прерывания, при котором активизируется соответствующий сигнал подтверждения прерывания INTA на одноименном выводе процессора.

~TEST вход:

Входной сигнал, поступающий на вывод TEST, проверяется командой процессора wait. Если сигнал на выводе TEST имеет значение логического 0, то команда wait функционирует так же, как команда nop. Если же сигнал на этом выводе имеет значение логической 1, то команда wait ожидает, пока сигнал на выводе TEST не станет низкого уровня. Этот вывод наиболее часто соединяется с цифровым сопроцессором 8087.

NMI вход:

Сигнал запроса немаскируемого прерывания, поступающий на вывод NMI (nonmaskable interrupt), аналогичен сигналу запроса прерывания INTR, за исключением того, что немаскируемое прерывание выполняется всегда и не зависит от установки бита управления прерыванием IF в регистре флагов. При активизации сигнала на входе NMI вызывается прерывание по вектору 2.

RESET вход:

Активный сигнал на выводе RESET возвращает микропроцессор в исходное состояние, если этот сигнал удерживается в течение не менее четырех периодов синхронизации процессора. Каждый раз при возврате микропроцессора в исходное состояние, начинается исполнение команд с ячейки памяти FFFF0H и последующие маскируемые прерывания становятся невозможными из-за очистки бита управления прерываниями IF в регистре флагов.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.