Курсовая работа

по дисциплине

«Моделирование»

|

Факультет: |

АВТ |

|

Группа: |

АМ-109 |

|

Студент: |

Пелевин Д.О. |

|

Преподаватель: |

Шалагинов А.В. |

|

Дата: |

Оглавление

1. Постановка задачи 3

2. Описание устройства 4

3. Проектирование в пакете DesignLab 8 5

3.1. Проектирование с использованием схемы замещения. 5

3.2. Проектирование с использованием макромодели. 12

4. Проектирование в пакете OrCAD 9.1 19

4.1. Проектирование с использованием схемы замещения. 19

4.2. Проектирование с использованием поведенческой модели. 23

6. Выводы 26

7. Список литературы 28

Данная работа преследует целью закрепление навыков проектирования цифровых узлов, полученных в ходе прослушивания курса лекций, лабораторных работ и выполнения РГР.

В ходе проектирования цифрового узла предполагается построение различных его моделей. С разработанном узле проводятся имитационные эксперименты, целью которых является подтверждение работоспособности узла и соответствие его временных задержек требуемым.

Необходимо спроектировать дешифратор ИД7.

|

|

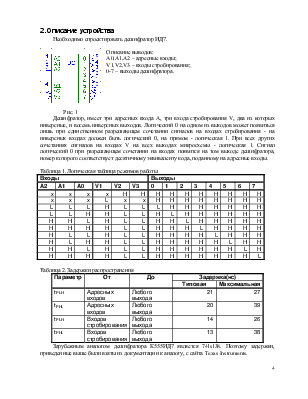

Описание выводов: A0,A1,A2 – адресные входы; V1,V2,V3 – входы стробирования; 0-7 – выходы дешифратора. |

|

Рис. 1 |

Дешифратор, имеет три адресных входа A, три входа стробирования V, два из которых инверсные, и восемь инверсных выходов. Логический 0 на одном из выходов может появиться лишь при единственном разрешающем сочетании сигналов на входах стробирования - на инверсных входах должен быть логический 0, на прямом - логическая 1. При всех других сочетаниях сигналов на входах V на всех выходах микросхемы - логическая 1. Сигнал логический 0 при разрешающем сочетании на входах появится на том выходе дешифратора, номер которого соответствует десятичному эквиваленту кода, поданному на адресные входы.

Таблица 1. Логическая таблица режимов работы

|

Входы |

Выходы |

||||||||||||

|

A2 |

A1 |

A0 |

V1 |

V2 |

V3 |

0 |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

|

x |

x |

x |

x |

H |

H |

H |

H |

H |

H |

H |

H |

H |

H |

|

x |

x |

x |

L |

x |

x |

H |

H |

H |

H |

H |

H |

H |

H |

|

L |

L |

L |

H |

L |

L |

L |

H |

H |

H |

H |

H |

H |

H |

|

L |

L |

H |

H |

L |

L |

H |

L |

H |

H |

H |

H |

H |

H |

|

H |

H |

L |

H |

L |

L |

H |

H |

L |

H |

H |

H |

H |

H |

|

H |

H |

H |

H |

L |

L |

H |

H |

H |

L |

H |

H |

H |

H |

|

H |

L |

L |

H |

L |

L |

H |

H |

H |

H |

L |

H |

H |

H |

|

H |

L |

H |

H |

L |

L |

H |

H |

H |

H |

H |

L |

H |

H |

|

H |

H |

L |

H |

L |

L |

H |

H |

H |

H |

H |

H |

L |

H |

|

H |

H |

H |

H |

L |

L |

H |

H |

H |

H |

H |

H |

H |

L |

Таблица 2. Задержки распространения

|

Параметр |

От |

До |

Задержка(нс) |

|

|

Типовая |

Максимальная |

|||

|

tPLH |

Адресных входов |

Любого выхода |

21 |

27 |

|

tPHL |

Адресных входов |

Любого выхода |

20 |

39 |

|

tPLH |

Входов стробирования |

Любого выхода |

14 |

26 |

|

tPHL |

Входов стробирования |

Любого выхода |

13 |

38 |

Зарубежным аналогом дешифратора К555ИД7 является 74ls138. Поэтому задержки, приведенные выше были взяты из документации к аналогу, с сайта Texas Instruments.

|

|

|

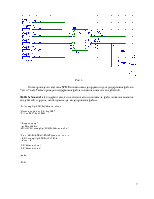

Рис. 2 УГО проектируемого узла |

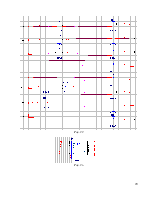

При реализации схемы замещения все элементы представлены в отечественных графических обозначениях по ЕСКД, в соответствие с требованиями к данной работе. Также надо отметить, что использовались реальные микросхемы. Схема замещения приведена на рис. 3.

|

|

Рис. 3 |

Схема тестирования приведена на рис. 4.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.