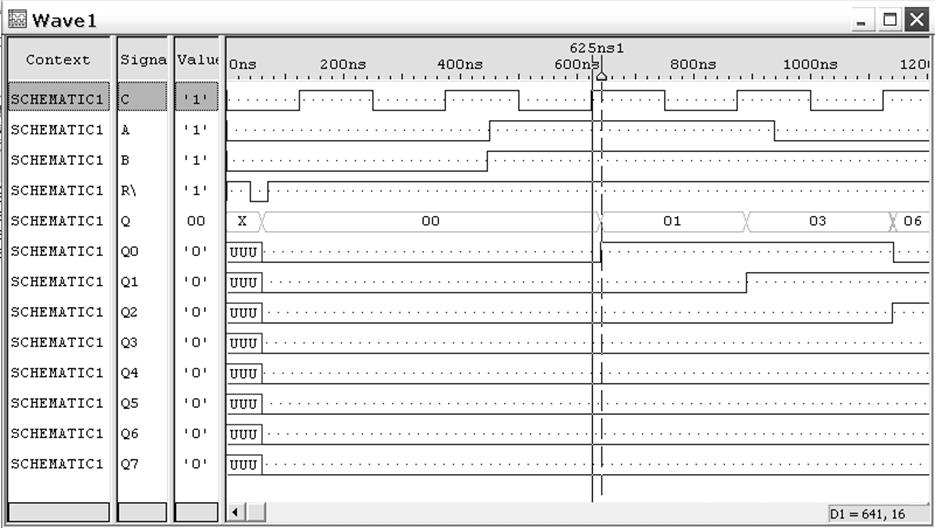

Рис. 25. Задержка распространения сигнала от входа С до выходов

при переключении из 0 в 1 – 16 нс.

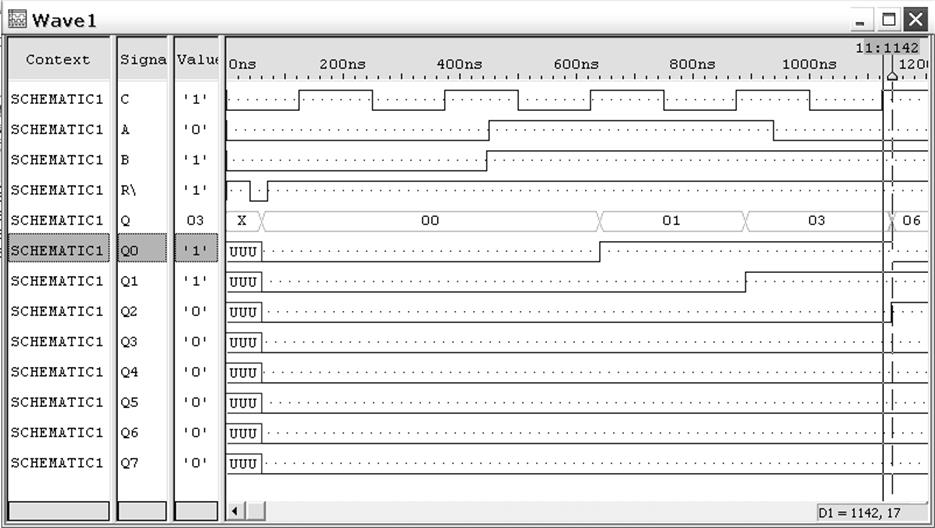

Рис. 26. Задержка распространения сигнала от входа С до выходов

при переключении из 1 в 0 – 17 нс.

Микросхема ИР8 занимает корпус DIP14 и как таковой упаковочной информации не требует, за исключением того, что при её создании нужно указать значение в опции “количество микросхем в корпусе” равное 1. Основной проблемкой при создании модели являлось вспоминание синтаксиса VHDL.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY KR1533IR8 IS PORT(

---Описание входов---

A : IN std_logic;

B : IN std_logic;

C : IN std_logic;

\R\\\ : IN std_logic;

---Описание выходов---

Q0 : OUT std_logic;

Q1 : OUT std_logic;

Q2 : OUT std_logic;

Q3 : OUT std_logic;

Q4 : OUT std_logic;

Q5 : OUT std_logic;

Q6 : OUT std_logic;

Q7 : OUT std_logic;

---входы питания и земли---

PWR : IN std_logic;

GND : IN std_logic

);

END KR1533IR8;

ARCHITECTURE model OF KR1533IR8 IS

---Создание временного сигнала Q_INT в виде 8-разрядной шины---

---сигнал Q_INT задается потому, что нельзя непосредственно---

---оперировать с переменными выхода (Q0,Q1,Q2,Q3,Q4,Q5,Q6,Q7)---

signal Q_INT : std_logic_vector (0 to 7);

begin

---Переменные (входы) учавствующие в моделировании---

process(A,B,\R\\\,C)

begin

---Условие сброса---

if \R\\\ = '0' then

Q_INT<="00000000" after 20ns;

---Условие, при котором происходит хранение---

elsif \R\\\ = '1' and C = '0' then

Q_INT(0 to 7) <= Q_INT(0 to 7) after 17ns;

---Условие А = 0, B=1 для сдвига влево с записью в старший разряд---

--- функции A&B. Сдвиг происходит по срезу синхросигнала---

elsif \R\\\ = '1' and A = '0' and B = '1' and C = '1' and C'EVENT then

Q_INT(0)<=(A and B) after 17ns;

Q_INT(1 to 7)<=Q_INT(0 to 6) after 17ns;

---Условие А = 1, B=0 для сдвига влево с записью в старший разряд---

--- функции A&B. Сдвиг происходит по срезу синхросигнала---

elsif \R\\\ = '1' and A = '0' and B = '1' and C = '1' and C'EVENT then

Q_INT(0)<=(A and B) after 17ns;

Q_INT(1 to 7)<=Q_INT(0 to 6) after 17ns;

---Условие для сдвига влево с записью в старший разряд функции A&B---

---Сдвиг происходит по фронту синхросигнала---

elsif \R\\\ = '1' and C = '1' and C'EVENT then

Q_INT(0)<=(A and B) after 16ns;

Q_INT(1 to 7)<=Q_INT(0 to 6) after 16ns;

end if;

end process;

---Присваиваем реальным выходам обработанный нами сигнал Q_INT

(Q0,Q1,Q2,Q3,Q4,Q5,Q6,Q7)<=Q_INT;

END model;

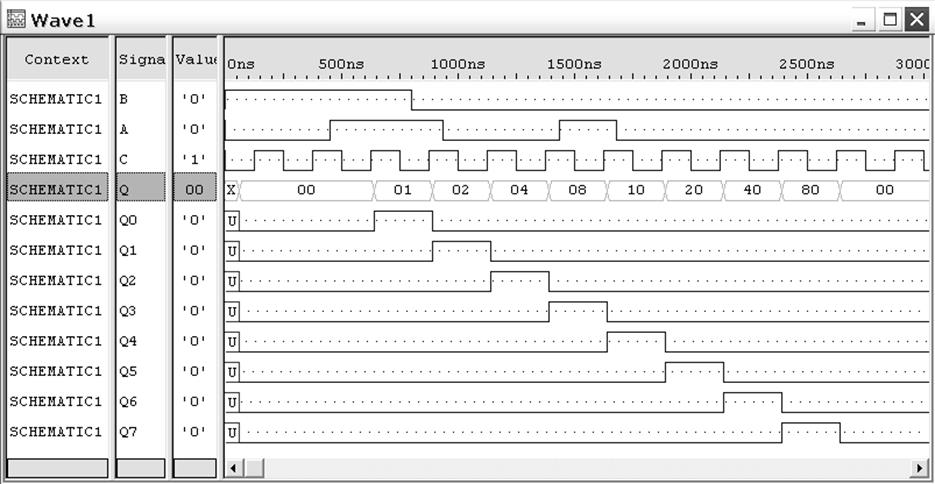

Рис. 27. Результаты работы поведенческой модели.

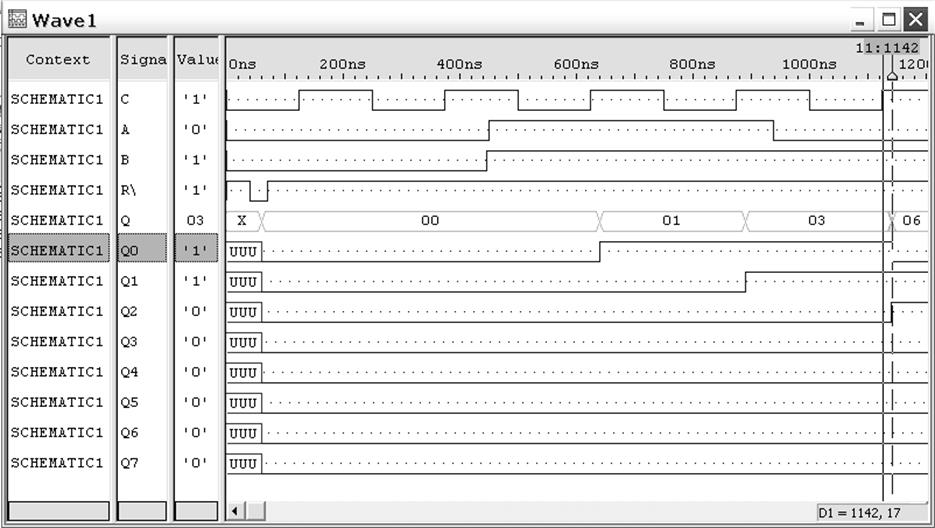

Рис. 28 . Задержка распространения сигнала от входа ~R до выходов

при переключении из 1 в 0 – 20 нс.

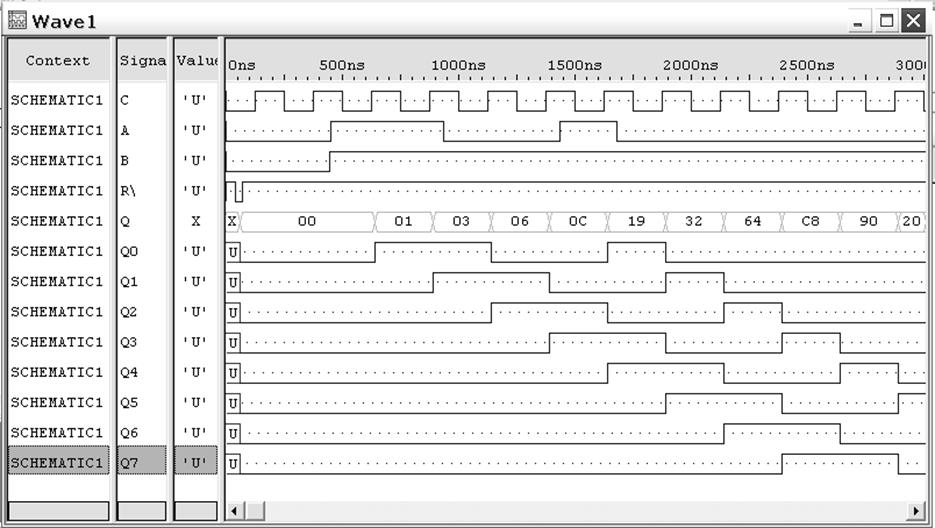

Рис. 29. Задержка распространения сигнала от входа С до выходов

при переключении из 0 в 1 – 16 нс.

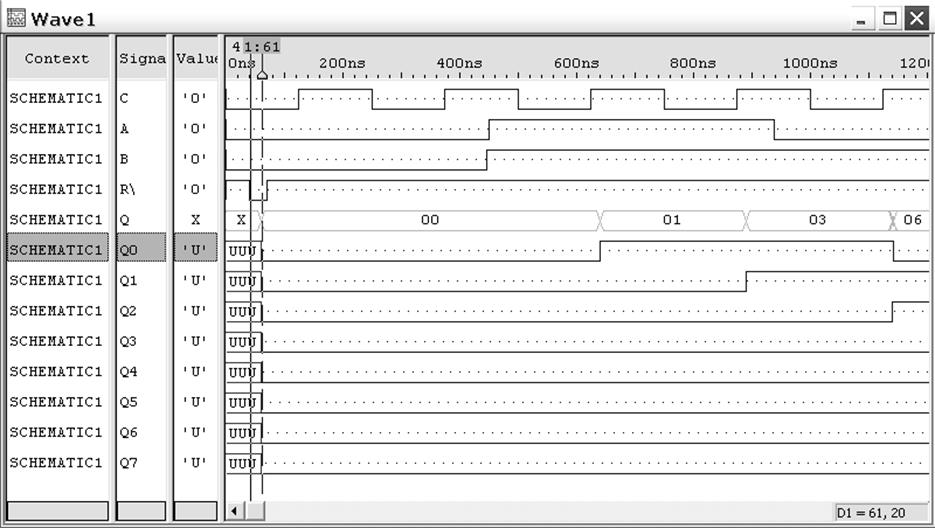

Рис. 30. Задержка распространения сигнала от входа С до выходов

при переключении из 1 в 0 – 17 нс.

В данной курсовой работе нужно было создать модели узла – функциональные и структурные в двух пакетах Designlab и OrCAD. По результатам работы можно провести сравнительный анализ двух пакетов в плане легкости их изучения и использования для создания, тестирования и отладки моделей цифровых устройств.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.