Наличие двух входов последовательной загрузки A и B позволяет использовать один из них в качестве управляющего загрузкой данных: низкий уровень напряжения хотя бы на одном из них по положительному фронту тактового импульса устанавливает первый триггер регистра в состояние низкого уровня напряжения, в то же время высокий уровень напряжения на управляющем входе позволяет по другому входу осуществлять ввод данных в последовательном коде.

Низкий уровень напряжения на входе ~R асинхронно устанавливает все выходы микросхемы в состояние низкого уровня напряжения..

Состояния схемы ИР8 приведены в табл. 2.

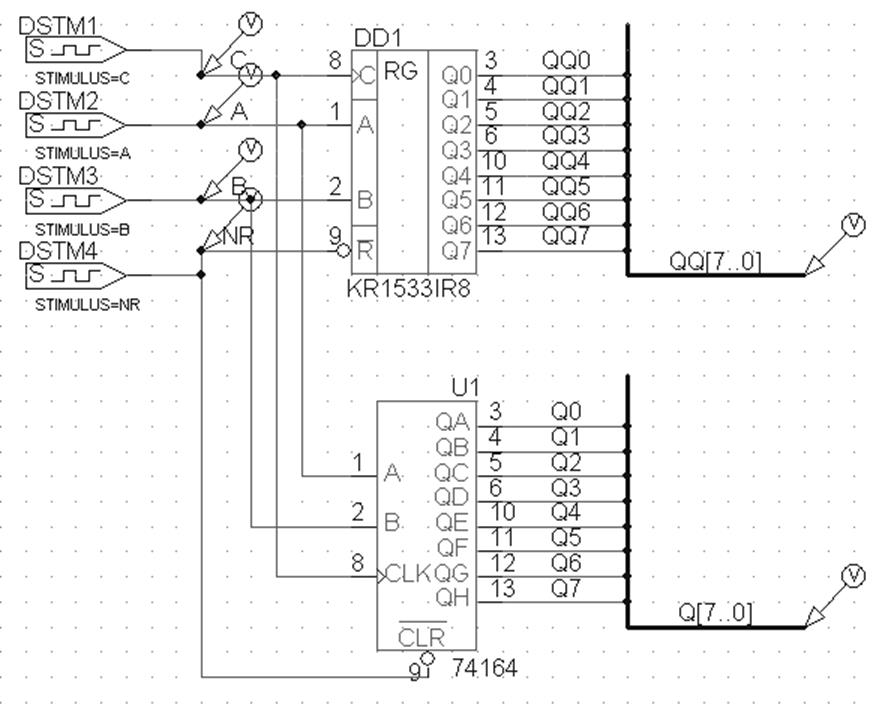

Рис. 2. Принципиальная схема ИР8, верификация с зарубежным аналогом.

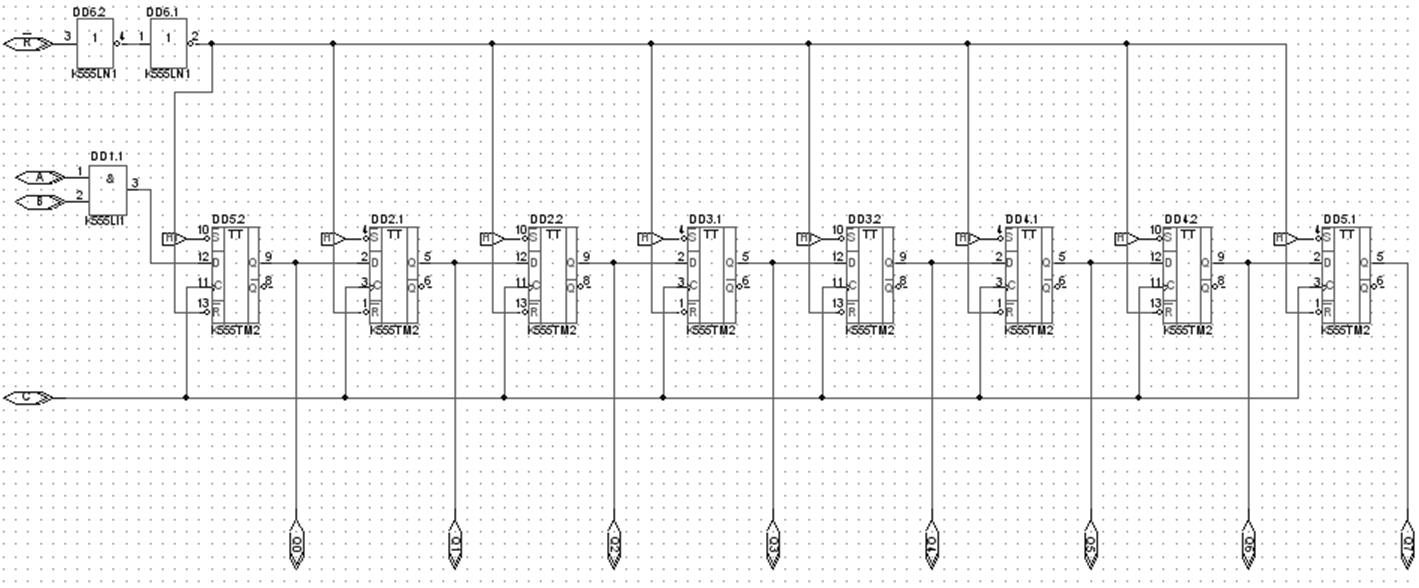

Рис. 3. Схема замещения ИР8

При создании схемы замещения использовались зарубежные элементы из системной библиотеки 7400.slb, преобразованные в соответствии с принятым ГОСТом и сохранены в личную библиотеку LIB.slb. В функциональных описаниях элементов (файл LIB.mod) пришлось заменить наименования элементов и имена входных и выходных портов. Основной трудностью оказалось подобрать задержки у элементов в схеме замещения так, чтобы правильно работал замещаемый регистр. Для облегчения решения задачи задержки у вентилей были приняты за 1ns. А у триггеров приближены максимально к реальным.

*-------------------------------------------------------------------------

* K555LN1 Hex Inverters

*

* The TTL Data Book, Vol 2, 1985, TI

* tdn 06/23/89 Update interface and model names

*

.subckt K555LN1 A2 Y

+ optional: DPWR=$G_DPWR DGND=$G_DGND

+ params: MNTYMXDLY=0 IO_LEVEL=0

U1 inv DPWR DGND

+ A2 Y

+ D_LN1 IO_STD MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

.ends

*

.model D_LN1 ugate (

+ tplhty=1ns tplhmx=1ns

+ tphlty=1ns tphlmx=1ns

+ )

*$

*-------------------------------------------------------------------------

* K555LI1 Quadruple 2-input Positive-And Gates

*

* The TTL Data Book, Vol 2, 1985, TI

* tdn 06/23/89 Update interface and model names

*

.subckt K555LI1 A1 B1 Y1

+ optional: DPWR=$G_DPWR DGND=$G_DGND

+ params: MNTYMXDLY=0 IO_LEVEL=0

U1 and(2) DPWR DGND

+ A1 B1 Y1

+ D_LI1 IO_STD MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

.ends

*

.model D_LI1 ugate (

+ tplhty=1ns tplhmx=1ns

+ tphlty=1ns tphlmx=1ns

+ )

*$

*-------------------------------------------------------------------------

* K555TM2 Dual D-Type Positive-Edge-Triggered Flip-Flops with Preset and Clear

*

* The TTL Data Book, Vol 2, 1985, TI

* tdn 06/28/89 Update interface and model names

*

.subckt K555TM2 1RBAR 1D 1C 1SBAR 1Q 1QBAR

+ optional: DPWR=$G_DPWR DGND=$G_DGND

+ params: MNTYMXDLY=0 IO_LEVEL=0

UFF1 dff(1) DPWR DGND

+ 1SBAR 1RBAR 1C 1D 1Q 1QBAR

+ D_TM2 IO_STD MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

.ends

.model D_TM2 ueff (

+ twpclmn=6ns twclklmn=10ns

+ twclkhmn=10ns tsudclkmn=5ns

+ thdclkmn=1ns tppcqlhmx=1ns

+ tppcqhlmx=18ns tpclkqlhty=1ns

+ tpclkqlhmx=16ns tpclkqhlty=1ns

+ tpclkqhlmx=17ns

+ )

*$

В этом файле хранится информация о схеме.

Test.cir

- Путь к моделируемой схеме

* E:\NSTU\Modelirovanie\Modelirovanie\bezz'ka\dl\TEST.sch

- Версия САПР на которой проводилось моделирование

* Schematics Version 8.0 - July 1997

- Дата моделирования

* Mon Dec 22 20:06:36 2003

- Шаг и конечное время моделирования

** Analysis setup **

.tran 20ns 4000ns

.OPTIONS DIGMNTYMX=3

- Путь к файлу с внешними воздействиями

.STMLIB "E:\NSTU\Modelirovanie\Modelirovanie\bezz'ka\dl\TEST.stl"

* From [SCHEMATICS NETLIST] section of msim.ini:

.lib "nom.lib"

- Подключенные библиотеки

.inc "E:\NSTU\Modelirovanie\Modelirovanie\bezz'ka\dl\LIB.mod"

.inc "E:\NSTU\Modelirovanie\Modelirovanie\bezz'ka\dl\KR1533IR8.lib"

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.