USE

ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY K555LN1 IS PORT(

---Описание входов и

выходов с упаковочной информацией---

\IN_-1\ : IN std_logic;

\IN_-2\ : IN std_logic;

\IN_-3\ : IN std_logic;

\IN_-4\ : IN std_logic;

\IN_-5\ : IN std_logic;

\IN_-6\ : IN std_logic;

\Y_-1\ : OUT std_logic;

\Y_-2\ : OUT std_logic;

\Y_-3\ : OUT std_logic;

\Y_-4\ : OUT std_logic;

\Y_-5\ : OUT std_logic;

\Y_-6\ : OUT std_logic;

---Описание контактов

питания и земли---

PWR : IN std_logic;

GND : IN std_logic);

END K555LN1;

ARCHITECTURE model OF

K555LN1 IS

BEGIN

---Функция выхода для

первой секции---

\Y_-1\ <= NOT \IN_-1\ AFTER 1 ns;

---Функция выхода для

второй секции---

\Y_-2\ <= NOT \IN_-2\ AFTER 1 ns;

---Функция выхода для

третьей секции---

\Y_-3\ <= NOT \IN_-3\ AFTER 1 ns;

---Функция выхода для

четвёртой секции---

\Y_-4\ <= NOT \IN_-4\ AFTER 1 ns;

---Функция выхода для

пятой секции---

\Y_-5\ <= NOT \IN_-5\ AFTER 1 ns;

---Функция выхода для

шестой секции---

\Y_-6\ <= NOT \IN_-6\ AFTER 1 ns;

END model;

--------------------------------------

-------MODEL

K555TM2-------

--------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use IEEE.NUMERIC_STD.all;

LIBRARY ieee;

USE

ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY K555TM2 IS PORT(

\D_-1\ : IN std_logic;

\D_-2\ : IN std_logic;

\C_-1\ : IN std_logic;

\C_-2\ : IN std_logic;

\Q_-1\ : OUT std_logic;

\Q_-2\ : OUT std_logic;

\Q\\_-1\ : OUT std_logic;

\Q\\_-2\ : OUT std_logic;

PWR : IN std_logic;

\S_-1\ : IN std_logic;

\S_-2\ : IN std_logic;

GND : IN std_logic;

\R_-1\ : IN std_logic;

\R_-2\ : IN std_logic);

END K555TM2;

ARCHITECTURE model OF

K555TM2 IS

begin

---Описание

сигналов учавствующих в моделировании---

process(\D_-1\,\R_-1\,\S_-1\,\C_-1\,\D_-2\,\R_-2\,\S_-2\,\C_-2\)

BEGIN

---Первая

секция---

---Условие сброса---

if \R_-1\ = '0' then

\Q_-1\<='0'

after 18ns;

\Q\\_-1\<='1'

after 18ns;

---Условие

установки в 1---

elsif \S_-1\

= '1' then

\Q_-1\<='1' after 18ns;

\Q\\_-1\<='0'

after 18ns;

---Описание

работы D-триггера---

elsif \C_-1\ = '1' and \C_-1\'EVENT then

if

\D_-1\ = '0' then

\Q_-1\<=\D_-1\

after 17ns;

\Q\\_-1\<=

not \D_-1\ after 17ns;

elsif

\D_-1\ ='1' then

\Q_-1\<=\D_-1\

after 16ns;

\Q\\_-1\<=not

\D_-1\ after 16ns;

end

if;

end

if;

---Вторая

секция---

if

\R_-2\ = '0' then

\Q_-2\<='0'

after 18ns;

\Q\\_-2\<='1'

after 18ns;

---Условие

установки в 1---

elsif \S_-2\ = '1' then

\Q_-2\<='1'

after 18ns;

\Q\\_-2\<='0'

after 18ns;

elsif

\C_-2\ = '1' and \C_-2\'EVENT then

if

\D_-2\ = '0' then

\Q_-2\<=\D_-2\

after 17ns;

\Q\\_-2\<=

not \D_-2\ after 17ns;

elsif

\D_-2\ ='1' then

\Q_-2\<=\D_-2\

after 16ns;

\Q\\_-2\<=not

\D_-2\ after 16ns;

end

if;

end

if;

end process;

END model;

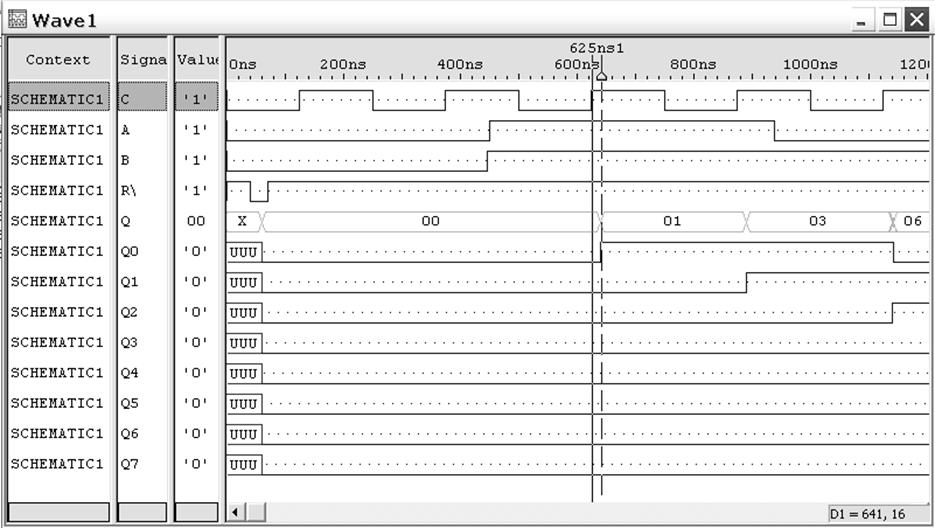

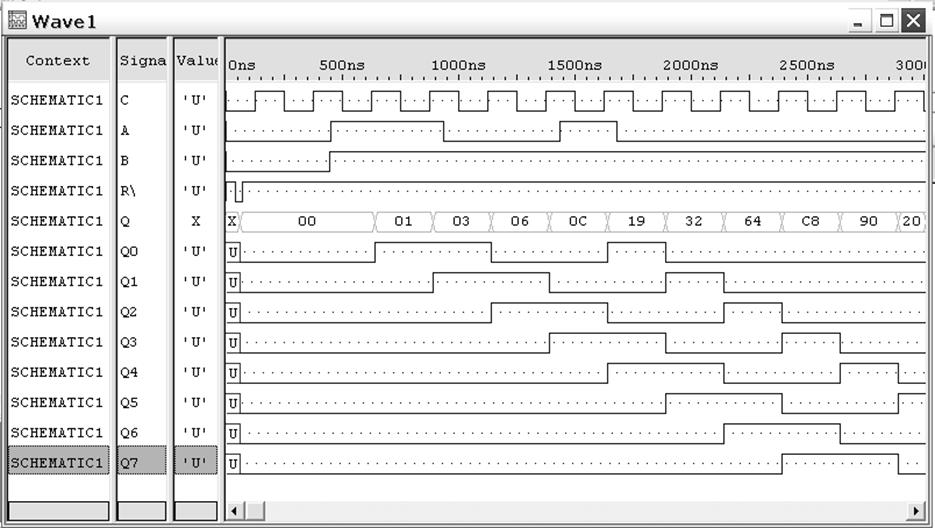

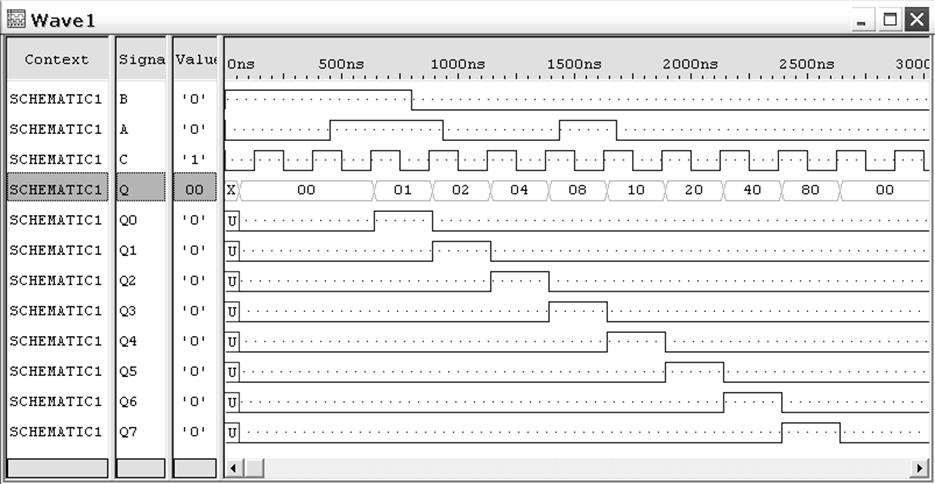

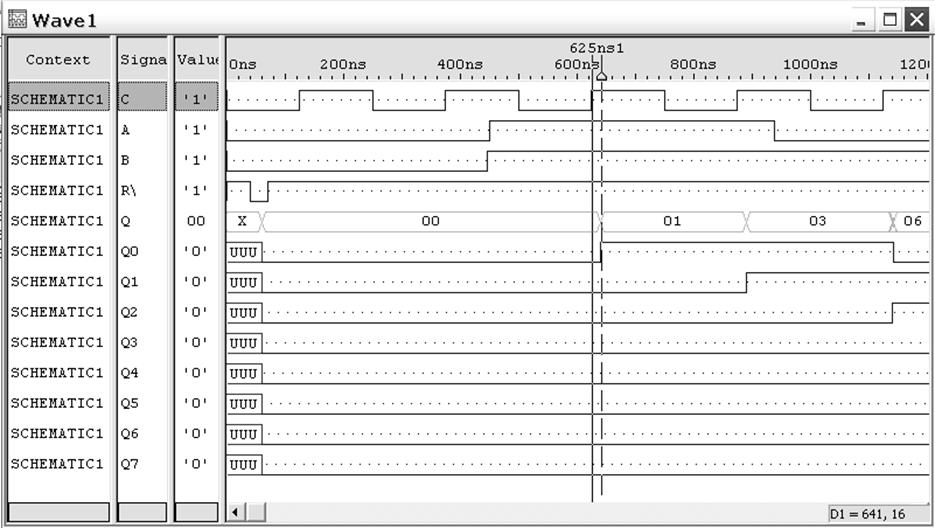

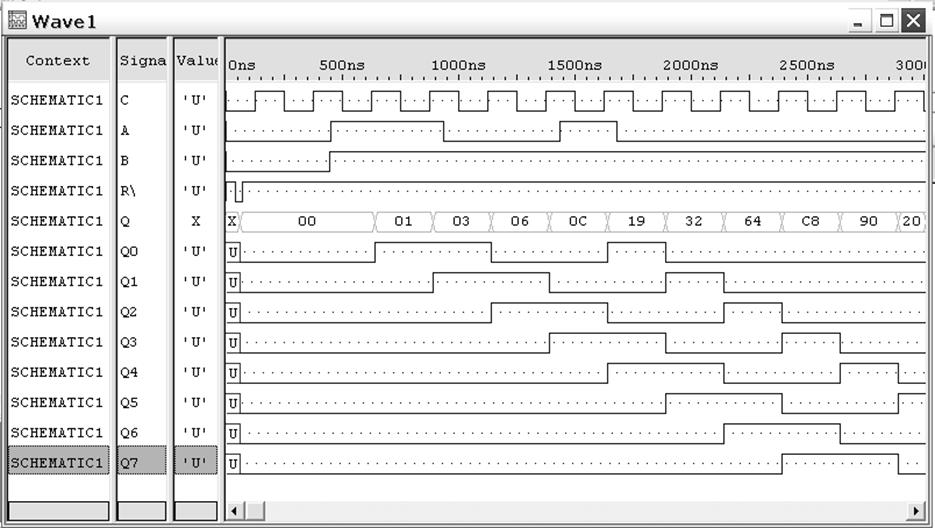

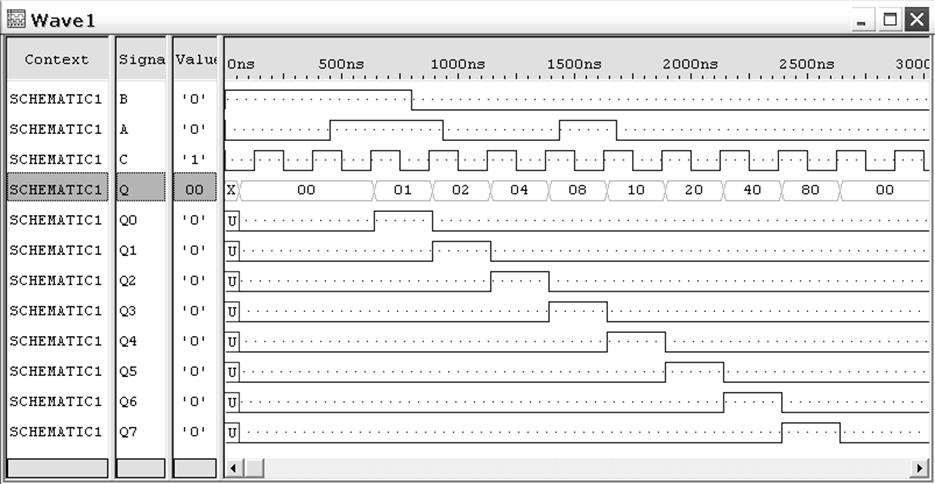

Результаты работы схемы замещения.

Рис. 23. Результаты работы схемы замещения.

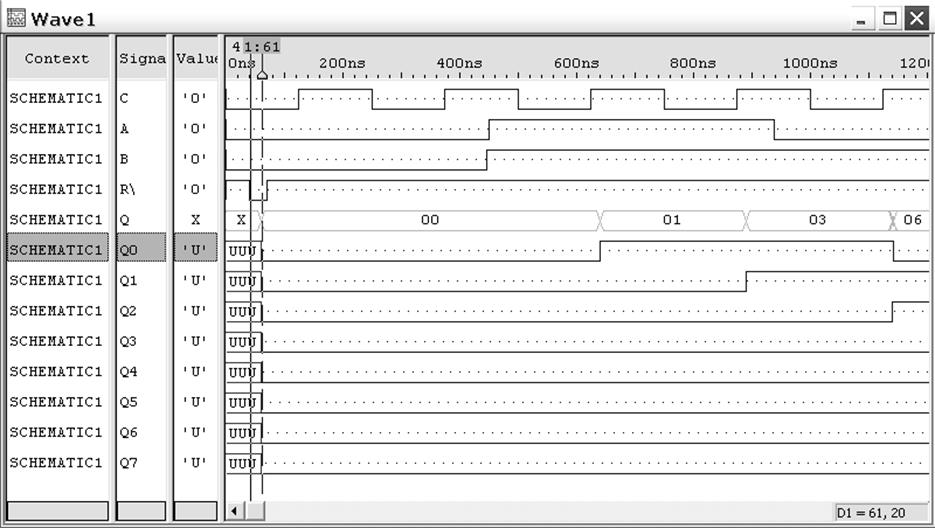

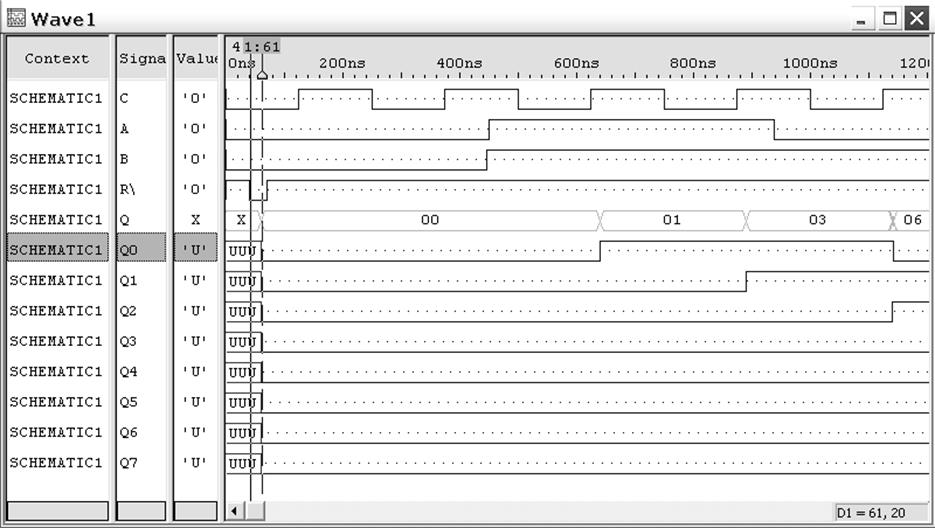

Рис. 24. Задержка распространения сигнала от входа ~R до выходов

при переключении из 1 в 0 – 20 нс.