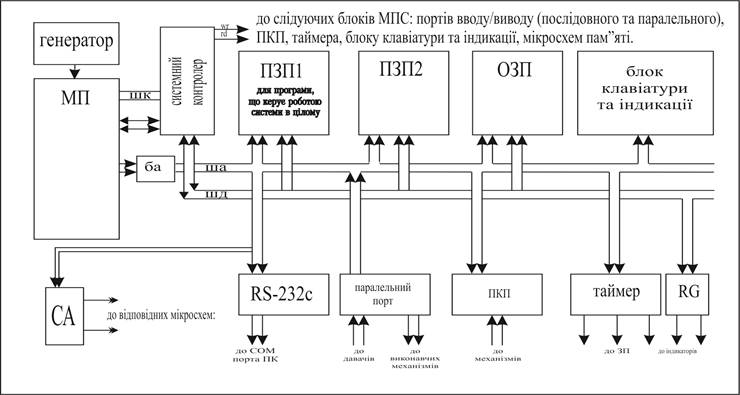

· Мікропроцесор (МП) – призначений для виконання арифметико-логічних операцій по наперед-заданій програмі.

· Буфер адреси (БА) – призначений для зовнішньої буферизації адреси, складається з буферних регістрів.

· Системний контролер (СК) – використовується для зовнішнього буферування шини даних і формування так званої роздільної шини керування.

· Постійний запам’ятовуючий пристрій (ПЗП) – призначений для зберігання найчастіше виконуваних команд, кодування інформації та перетворення кодів.

· Оперативно-запам’ятовуючий пристрій (ОЗП) – призначений для зберігання інформації. Структурні схеми ОЗП та ПЗП аналогічні. Відрізняються тільки типом комірок пам’яті та сигналами керування. ОЗП поділяють на статичні та динамічні.

· Програмований контролер переривань (ПКП) – призначений для спряження (підключення) декількох зовнішніх пристроїв, які можуть викликати переривання.

· Програмований паралельний інтерфейс (ППІ) – призначений для зв’язку зовнішніх пристроїв з системою як пристрою паралельної передачі інформації.

· Блок індикаторів (БІ) – призначений для індикації.

|

Мікросхема КР580ВМ80А – функціонально закінчений однокристальний паралельний 8-розрядний мікропроцесор з фіксованою системою команд, застосовується в якості центрального процесора в пристроях обробки даних і управління.

Мікропроцесор має роздільний 16-розрядний канал адреси і 8-розрядний канал даних. Канал адреси забезпечує пряму адресацію зовнішньої пам'яті об’ємом до 65536 байт, 256 пристроїв введення і 256 пристроїв виводу.

Умовне графічне позначення мікросхеми приведено на рисунку 2.2, призначення виводів – в таблиці 2.1, структурна схема показана на рисунку 2.3.

|

Рисунок 2.2 - Умовне графічне позначення мікропроцесора КР580ВМ80А

Восьмирозрядний арифметико-логічний пристрій мікропроцесора забезпечує виконання арифметичних і логічних операцій над двійковими даними, приведених в додатковому коді, а також обробку двійково-десяткових упакованих чисел.

До складу блоку регістрів входять:

· 16-розрядний регістр адреси команди (IP),

· 16-розрядний регістр показника стека (SP),

· 16-розрядний регістр тимчасового зберігання (WZ),

· 16-розрядна схема інкремента-декремента і

· шість 8-розрядних регістрів загального призначення (B, C, D, E, H, L), які можуть використовуватись і як три 16-розрядні регістри (BC, DE, HL).

Мікропроцесор виконує команди по машинних циклах. Число циклів, необхідне для виконання команди, залежить від її типу і може бути від одного до п'яти. Машинні цикли виконуються по машинних тактах. Тривалість такту рівна періоду тактової частоти і при частоті 2,0 МГц складає 500 нс.

На початку кожного машинного циклу мікропроцесор виробляє сигнал синхронізації SYN, який в поєднанні із іншими сигналами може бути використаний для організації різних режимів роботи.

Після подачі на вихід SR сигналу високого рівня мікропроцесор встановлюється в початковий стан. В такті Т1 мікропроцесор видає на адресний канал адресу комірки, в якій зберігається команда програми, а через канал даних – інформацію про стан. В такті Т2 аналізується стан сигналів на вході RDY, «Підтвердження зупинки» і залежно від стану цих сигналів МП переходить в стан очікування, зупинки або до виконання такту Т3. В такті Т3 за наявності сигналу високого рівня на вході RDY МП приймає інформацію по каналу даних; аналізує стан сигналу на вході HLD і якщо цей сигнал високого рівня, то після завершення такту Т3 переходить в стан захоплення. Залежно від коду команди, що виконується, машинний цикл завершується після виконання тактів Т3, Т4 або Т5.

Таблиця 2.2- Призначення виводів КР580ВМ80А

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.