Для такого дільника справедливі наступні співвідношення:

![]()

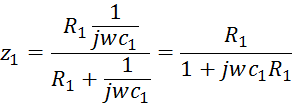

При цьому величина комплексних опорів будуть рівні:

відповідно

![]()

тоді

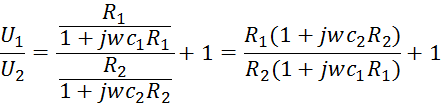

Виходячи

з останнього виразу можна зробити висновок, що співвідношення

![]() є

справедливим в тому випадку коли R1C1=R2C2.

є

справедливим в тому випадку коли R1C1=R2C2.

Аналітичний висновок можна зробити і для багато ланцюгового дільника. Таким чином буде справедливе співвідношення C1R1=C2R2=CnRn.

Оскільки величина ємності C1 визначається в основному вхідна ємність приладу, то вона приймається рівною не більше 20nФ.

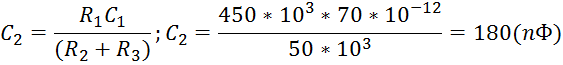

На першій границі вимірювання є справедливим наступне співвідношення:

![]()

Ємність конденсатора C1 визначається як:

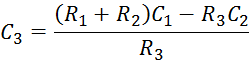

Величина ємності C3 визначається з рівності:

![]()

звідси

![]()

Виходячи з мінімального значення температурного коефіцієнта ємності (ТКЄ), вибираємо компенсатор C1-C3 типу КСО. Оскільки в номінальному ряді серійних конденсаторів з такими ємностями немає, то їх величини реалізуються нобором.

9. Опис принципової схеми.

Аналоговий сигнал з максимальною амплітудою до 4В поступає на аналоговий вхід АЦП (D, вхід 17). Одночасно цей сигнал поступає через резистор R2 на схему виділення періоду вхідного сигналу, яка складається з компаратора D2 і тригера D3.

Тривалість імпульсів на прямому вході тригера рівна тривалості (періоду) вхідного сигналу.

Так як АЦП має в своєму стані регістри з трьома станами, то його цифрові виходи підключаються на ШД без буферування.

Використано в схемі тактовий генератор КР1810ГФ84. Навантажувана здатність мікропроцесора досить мала, тому необхідно буферувати ШД і ША. Для буферування ША використано регістри КР580ИР82 (мікросхеми D6, D7). По сигналу STB МП адреса записується в ці буфери. Перехід ША в третій стан здійснюється по сигналу HLDA МП. Для буферування ШД використовуються буфери D8, D9.

Сигналом DE мікропроцесора виходи буфера підключаються до ШД. Сигнал OP/IP вказує на напрям передачі даних.

Постійний запам’ятовуючий пристрій виконаний на мікропроцесорах D11, D12. Адресні входи під’єднані до ША, а виводи даних до ШД. Для спрощення всі шини об’єднані в одну системну магістраль. Так як ПЗП використовується тільки для читання, то на вхід WE необхідно подати +5В. Читання з ПЗП здійснюється по сигналах RD на /IO МП. Включення мікросхеми виконується сигналом A11 (від ША). Якщо А11=«0», то мікросхема включена.

ОЗП виконаний на мікросхемах D13,D14.

Включення мікросхеми відбувається сигналом А11 високого рівня. По шинах МП RD, WR, M1/IO здійснюється читання та запис в пам'ять.

В даній АЦП, порт виводу, прапорець готовності відносяться до зовнішніх пристроїв. Для того, щоб їх розрізняти, вводимо дешифратор адреси (мікросхема D15). Принцип перетворення полягає в тому, що МП спочатку читає прапорець і перевіряє, чи є «1» на вході 5 мікросхеми D3 (початок періоду). Якщо ні, то МП продовжує перевіряти (чекає «1»). З появою на вході 5 D3 «1» МП видаю сигнал запуску АЦП, який починає перетворювати вхідний сигнал. Готовність даних ініціалізується появою сигналу RDY на виході 11 мікросхеми D5. По цьому сигналу МП подає команду на вхід 24 DE АЦП і дані з АЦП виставляється на ШД і читається мікропроцесором. Якщо на вході 5 тригера D3 появиться «0» (кінець періоду), то після обраховується значення Uсерквадр. і заносяться в оперативну пам'ять (в масив). Після того як буде обраховано 500 значень Uсерквадр. з масиву даних визначається мінімальне і середнє значення і видається у порти виводу.

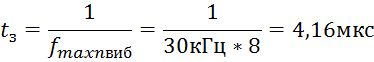

Між вибірками організовується затримка, яка становить:

Із значення частоти кількість вибірок збільшуєть.

Програму і алгоритми роботи див. додатки.

10. Короткий опис архітектури МП К1810ВМ86

Блок виконання команд 16 розрядний АЦП з регістром стану і пристроями управління, а також регістри загального призначення. Всі регістри і внутрішні магістралі блоку 16 розрядні. На АЦП поступають коди команд з конвеєра команд.

Блок спряження з магістралями проводить всі пересилки даних і кодів.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.