Figure 4.5 Окружение GPRenv конструкции DLXσ

Окружения памяти

Конструкция DLX которая подготовлена для конвейерного выполнения включает два блока памяти, один для команд и один для фактического доступа к данным.

Окружение IMenv памяти команд управляется одним сигналом fetch, который активирует сигнал чтения Imr. Адрес доступа к памяти команд определен в регистре DPC. Таким образом, при fetch = 1, окружение IMenv выполняет операцию чтения, обеспечивающую слово памяти

IMout = IMword[(DPC[31 : 2]00)].

Так как память IMне выполняет доступа по записи, ее сигнал записи Imwвсегда неактивен.1 Управление IMCпамятью команд простое и имеет нулевую стоимость и задержку. Пусть dImemозначает время доступа к банку памяти IM. Так как адрес непосредственно берется из регистра, окружение IMenv задерживает выборку команды на

DIMenv(IR) = DIMC + dImem = dImem.

Память команд также обеспечивает сигнал ibusyпоказывающий, что доступ не может быть закончен в текущем тактовом цикле. Мы ожидаем, что этот сигнал будет верным через dIstatединиц времени после начала обращения к памяти IM.

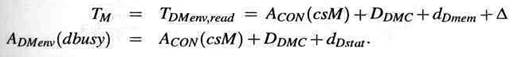

Окружение DMenv памяти данных DM выполняет обращение к памяти команд загрузки и записи. По большему счету, DMenv идентичен окружению памяти последовательной конструкции, но теперь адрес всегда обеспечивается регистром MAR.

Окружение DMenv управляется двумя сигналами Dmrи Dmw, которые запрашивают доступ к памяти по чтению или записи соответственно. Память

1Конечно это абстракция. В главе 6 мы обрабатываем кэш команд, который, конечно, может быть записан.

DM адресуема побайтно, управление DMC генерирует четыре сигнала записи в банк Dmbw[3 : 0] основываясь на адресе и ширине доступа по записи, как и в последовательной конструкции. Стоимость и задержка управления памятью остаются теми же самыми .

Память данных DM имеет время доступа dDmemи обеспечивает флаг dbusyс задержкой dDstat. Сигнал dbusyпоказывает, что текущее обращение не может быть закончено в текущем тактовом цикле. Пусть acon(csm) означает накопленную задержку сигналов Dmrи Dmw, тогда

Окружение PC

Окружение PCenv на рисунке 4.6 управляется семью сигналами управления, а именно:

• reset, который инициализирует регистры PC' и DPC,

• сигналы синхронизации PCceи linkce,

• jump, который обозначает одну из четырех команд перехода j, jal, jr и jalr,

• jumpR , который обозначает команды абсолютного перехода (jr, jalr),

• branch , который обозначает команды ветвления beqz, bnez,

• bzero , который активен при beqz и неактивен при bnez.

Основываясь на этих сигналах, gluelogicPCglueгенерирует тактовый сигнал для регистров PC' и DPC. Они синхронизируются одновременно, когда сигнал PCceактивен или при сбросе, то есть

PCce \/ reset.

В добавок, PCglueпроверяет операнд A' на ноль

AEQZ = 1 <-> [A[31:0]] = 0

и генерирует сигнал bjtakenсогласно спецификациям раздела 4.1. Таким образом, bjtakenустанавливается при любых переходах или принятии ветвления:

bjtaken = jump \/ branch /\ (bzero XNOR AEQZ).

|

|

Рисунок 4.6 Окружение PCenv осуществляющее задержанный PC

Пусть Acon(csID) означает накопленную задержку управляющих сигналов, которые управляют этапом ID. Тогда стоимость glue logic и задержка сигналов AEQZи bjtaken

CPCglue = 2*Cor + Cand + Cxnor + Czero(32)

DPCglue = Dor + Dand + Dxnor

A(AEQZ) = AGPRenv(A')+Dzero(32)

A(bjtaken) = max {ACON(csID),A(AEQZ)} + DPCglue.

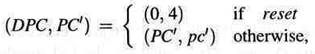

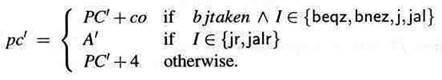

Окружение PCenv простейшим способом осуществляет механизм “задержанного PC” из раздела 4.1. При активном сигнале синхронизации, эти два PC установлены в

где значение pc' = nextPC(PC', А', со) команды I, которая содержится в регистре IR, вычисляется как

PCenv также обеспечивает регистр link , который обновляется под управлением сигнала linkce. При linkce= 1, он установлен в

link = PC' + 4,

это PC, который будет сохранен в случае команд перехода и связи.

|

|

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.