|

Теорема 4.2 |

Пусть конструкция DLX выполнена так, что

Таблица 4.5 RTL команды этапа EX

|

Состояние |

RTL команды |

активные управляющие сигналы |

|

Alu |

MAR = A op B, Cad.3 = Cad.2 |

bmuxsel, ALUDdoe, MARce, Rtype, Cad3ce |

|

Test |

MAR=(A rel B ? 1 :0), Cad.3 = Cad.2 |

bmuxsel, ALUDdoe, MARce, test, Rtype, Cad3ce |

|

Shift |

MAR = shift(A,B[4:0]), Cad.3 = Cad.2 |

bmuxsel, SHDdoe, MARce, Rtype, Cad3ce |

|

aluI |

MAR = A op со, Cad.3 = Cad.2 |

ALUDdoe, MARce, Cad3ce |

|

testI |

МAR=(A геl со ? 1 :0), Cad.3 = Cad.2 |

ALUDdoe, MARce, test, Cad3ce |

|

shiftI |

MAR = shift(A,co[4:0]), Cad.3 = Cad.2 |

SHDdoe, MARce, shiftI, Rtype, Cad3ce |

|

savePC |

MAR = link, Cad.3 = Cad.2 |

linkDdoe, MARce, Cad3ce |

|

addrL |

MAR = A + со, Cad.3 = Cad.2 |

ALUDdoe, add, MARce, Cad3ce |

|

addrS |

MAR = A + со, MDRw = cls(B,MAR[l:0]000) |

ALUDdoe, add, MARce, amuxsel, shift4s, MDRwce |

|

noEX |

1. для каждого типа команд берутся пути, определенные в таблице 4.8,

2. для каждого состояния s выполняется набор RTL команд rtl(s).

Если каждое обращение к памяти занимает только один такт, тогда машина интерпретирует набор команд DLX с семантикой задержанного PC.

Верность всех конвейерных машин в этой главе следует из теоремы. Добавление механизма останова из главы 3.4.3 заботится о обращениях к памяти, которые требуют более чем один цикл.

4.2.3 Управление вычисляемое заранее

Мы получим из вышеупомянутой FSD и простого механизма останова новые механизм управления и механизм останова с точно таким же поведением. На этом заканчивается конструирование подготовленной последовательной машины DLXσ .

Таблица 4.6 RTL команды этапов памяти и обратной записи

|

состояние |

RTL команда |

управляющие сигналы |

|

|

M |

passC |

С = MAR, Cad A = Cad.3 |

Cce, Cad4ce |

|

load |

MDRr = Mword[(MAR[31 : 2]00)], С = MAR, Cad A = Cad.3 |

Dmr, MDRrce, Cce, Cad4ce |

|

|

store |

т = bytes(MDRw) |

Dmw |

|

|

noM |

|||

|

WB |

sh41 |

GPR(Cad.4] = sh4l(MDRr,MAR[1 : 0]000) |

shift41, GPRw |

|

wb |

GPR[Cad.4] = С |

GPRw |

|

|

noWB |

(no update) |

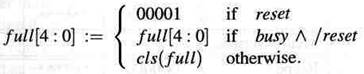

Мы начнем с механизма останова, который синхронизирует все этапы в round robin fashion. Это 5-битный регистр full[4 : 0], где для всех этапов iсигнал

uel = fulll /\ /busy

разрешает обновление регистров в out(i). Так как обращения к памяти могут занимать несколько тактов, обновление памяти данных DM разрешается full3 , а не ue3. Регистр fullобновляется

Так как конструкция включает два блока памяти, сигнал занято

/busy = ibusy NOR dbusy.

С сигналами fullопределенными таким образом, мы, очевидно, можем следить за этапом, который выполняет команду, а именно: команда находится на этапе i тогда и только тогда, когда fulli = 1. В частности, команда на этапе IFтолько когда full0 = 1, а на этапе ID, если full1 = 1. Мы преобразуем FSD следующими четырьмя изменениями:

1. Управляющие сигналы, активированные в состоянии IFтеперь всегда активны. В такте с full0 = 1 эти сигналы имеют верные значения. В других тактах они не имеют значения, поскольку IRне тактируется.

2. Сигналы Мура активированные в состоянии IDтеперь всегда активны. Они имеют значение только в тактах с full1 = 1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.