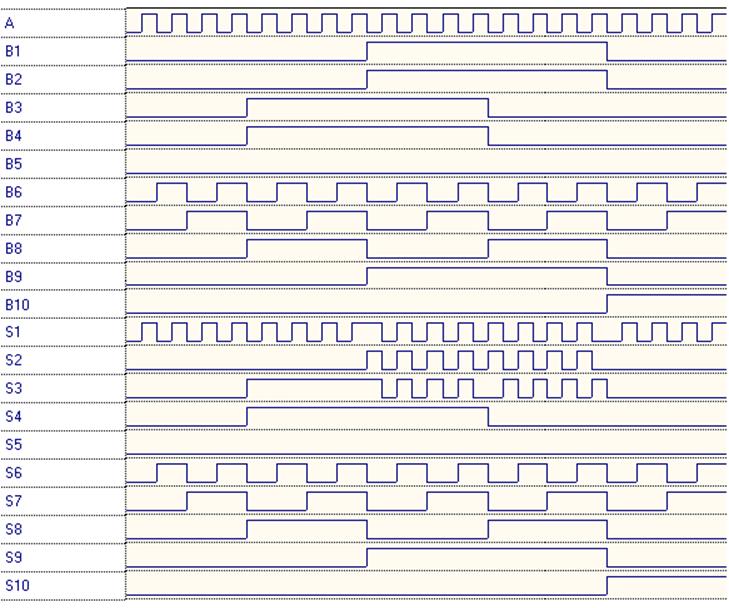

Рисунок 39 – Диаграмма состояний сумматора.

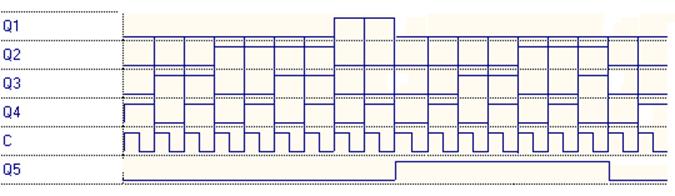

Рисунок 40 – Временная диаграмма работы счётчика.

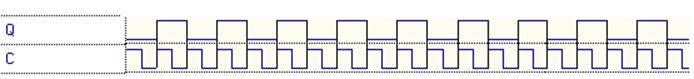

Рисунок 41 – Временная диаграмма работы делителя частоты.

4 Компоновка устройства

При компоновке различных типов устройств (аналоговых, цифровых, комбинированных и т.д.) из отдельно спроектированных блоков необходимо решать задачи по согласованию различных входных и выходных параметров (согласование выход-вход).

При построении аналоговых устройств согласуются входные/выходные сопротивления, напряжения, токи. Иногда учитываются также временные характеристики блоков.

При построении же цифровых устройств, при условии того, что компонентная база блоков однородна (обычно это значит, что микросхемы выбраны из одной серии), согласование аналоговых параметров (сопротивления, напряжения, токи) не производится. В данном случае необходимо учитывать только временные задержки «возбуждение входа-реакция выхода» и при компоновке разрешить следующие виды проблем: «дребезг» выхода (возникает при неоднородных временных параметрах входn-выходm в отдельно взятых блоках; переходное состояние), рассогласование блоков с памятью (внутреннее нарушение, влияющее на основное состояние выхода; возникает при синхронизации двух последовательно соединённых блоков с памятью и одинакового типа динамической синхронизацией синхроимпульсами с одинаковой фазой и частотой, при этом последующий блок воспринимает при очередном такте предыдущее состояние предыдущего блока), рассогласование компонентов внутри блока (возникает при некоторой верхней граничной частоте синхроимпульсов; компоненты внутри блока, вследствие своих ненулевых времён реакции не успевают переключатся, в результате чего на выходе блока появляется непредсказуемая комбинации; особенно ярко данное свойство проявляется при наличии сложной обратной связи).

При решении проблемы «дребезга» выхода достаточно поставить выходной триггерный буфер, представляющий собой регистр памяти, синхронизируемый на запись синхроимпульсом, сдвинутым по фазе так, что запись происходит только при установившемся состоянии выхода. Фактически стабильный выходной сигнал «защёлкивается» на выходе до следующего стабильного состояния. Преимущество данного способа – простота реализации и точная параллельная передача на выход комбинации. Но есть и ограничение - данный способ актуален только при наличии синхронизации. При асинхронном случае необходимо вводить элементы задержки на выходы блоков с временем реакции, меньшим максимального времени реакции выхода блока. Указанный способ имеет существенный недостаток – необходима калибровка элементов задержки, причём элементы задержки в схеме расположены рассредоточено.

При

решении проблемы рассогласования блоков с памятью необходимо разделить по

времени в каждом такте (рассматриваем только синхронный случай) события

срабатывания отдельных блоков, т.е. синхроимпульс, поступающий на последующий

блок с памятью в каскаде, должен отставать по фазе от синхроимпульса,

поступающего на предыдущий, таким образом, чтобы основное состояние предыдущего

блока успело установится, перед его считыванием последующим блоком. Причём

время установления состояния всего устройства не должно превышать период его

тактирующих импульсов. В самом простом случае можно использовать, как элемент

задержки, инвертор, который осуществляет сдвиг фазы на ![]() .

Другой вариант – каскадное включение логических элементов (линия задержки),

причём временной сдвиг будет равен сумме задержек элементов в каскадной

цепочке. Возможно также использование интегрального компонента – интегральной

линии задержки (ИЛЗ).

.

Другой вариант – каскадное включение логических элементов (линия задержки),

причём временной сдвиг будет равен сумме задержек элементов в каскадной

цепочке. Возможно также использование интегрального компонента – интегральной

линии задержки (ИЛЗ).

Для решения проблемы рассогласования компонентов внутри блока, выбирают частоту тактирующих импульсов меньшую граничной частоты блока.

Произведём расчёт максимальных задержек вход-выход у блоков (см. конкретную схему в компонентной базе и описание используемых компонентов). При расчёте не будем учитывать частотные ограничения блоков, т. к. частота импульсов построенного генератора намного меньше граничной частоты любого из блоков.

Расчёт максимальных временных задержек счётчика.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.