Что же касается режимов работы компаратора. В зависимости от того, какое из двух сравниваемых чисел больше, высокий уровень сигнала появляется либо на выходе QQ1, либо на выходе QQ3. То есть если число А больше числа В, то на выходе QQ3 появляется «1». Или наоборот, если А меньше В, то «1» появляется на выходе QQ1. Если число А равно числу В, но на входе AGBIN или ALBIN появился высокий уровень сигнала, то соответственно на выходе QQ1 или QQ3 тоже будет высокий уровень сигнала. Выход QQ2 активен только в том случае, если активен вход AEBIN. Иначе работают два других выхода.

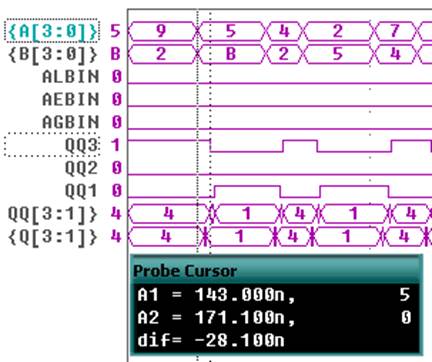

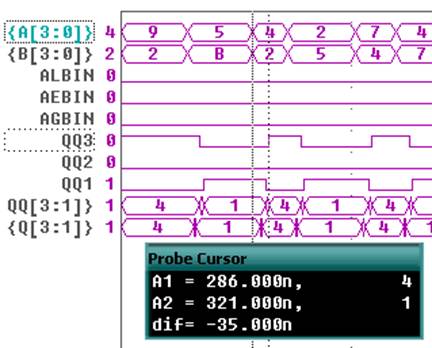

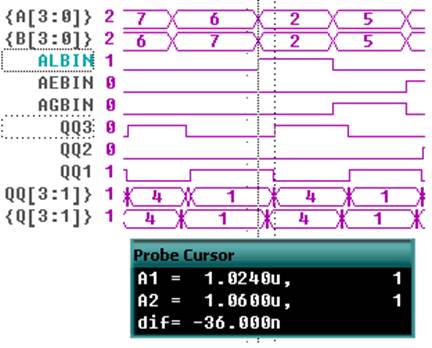

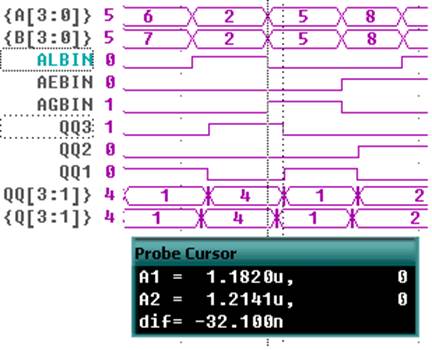

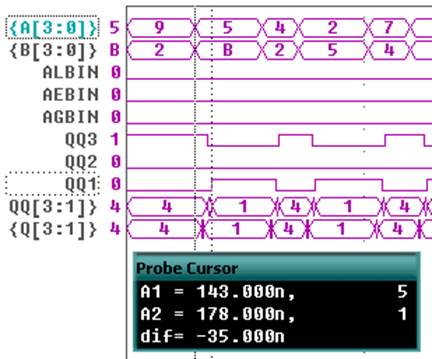

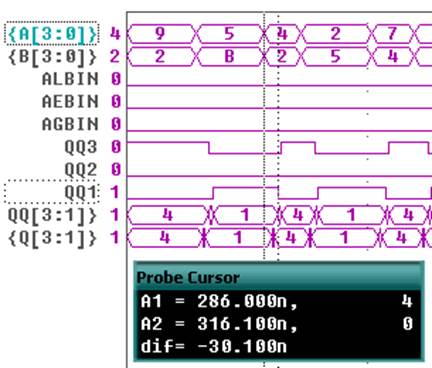

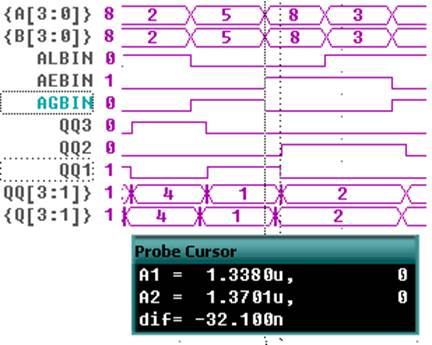

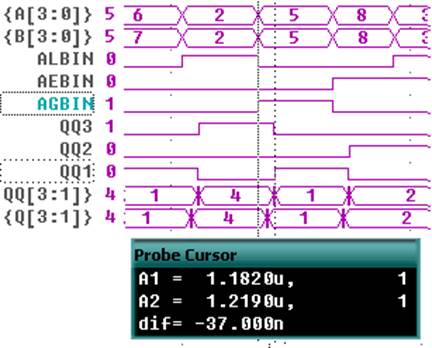

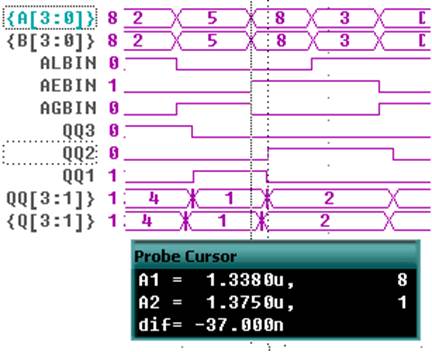

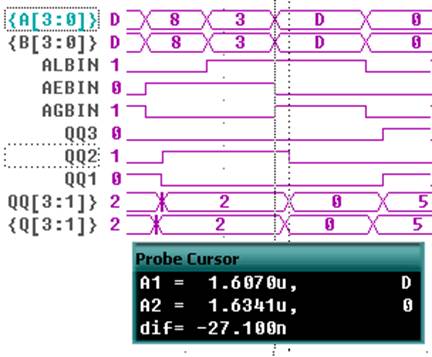

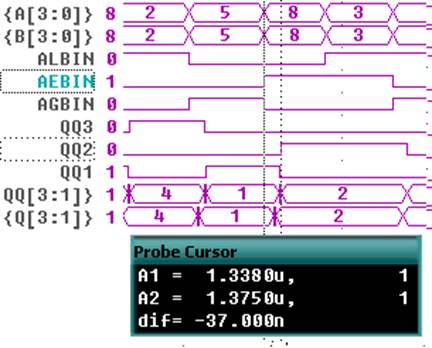

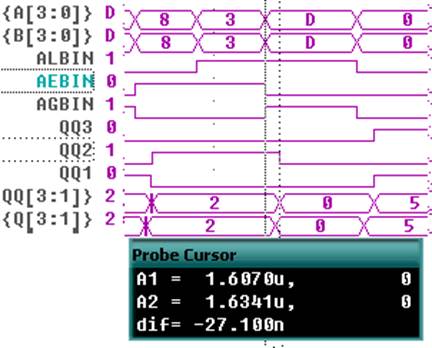

Далее представлены фрагменты временной диаграммы с различными задержками, приближенными к задержкам, описанными в таблице 3.

Рис. 6. Задержка распространения сигнала от входов А, В к выходу QQ3(A>B) при переключении из 1 в 0 ≈ 28 нс.

Рис. 7. Задержка распространения сигнала от входов А, В к выходу QQ3(A>B) при переключении из 0 в 1 ≈ 35 нс.

Рис. 8. Задержка распространения сигнала от входа ALBIN к выходу QQ3(A>B) при переключении из 0 в 1 – 36 нс.

Рис. 9. Задержка распространения сигнала от входа ALBIN к выходу QQ3(A>B) при переключении из 1 в 0 ≈ 32 нс.

Рис. 10. Задержка распространения сигнала от входов А, В к выходу QQ1(A<B) при переключении из 0 в 1 – 35 нс.

Рис. 11. Задержка распространения сигнала от входов А, В к выходу QQ1(A<B) при переключении из 1 в 0 ≈ 30 нс.

Рис. 12. Задержка распространения сигнала от входа АGВIN к выходу QQ1(A<B) при переключении из 1 в 0 ≈ 32 нс.

Рис. 13. Задержка распространения сигнала от входа АGВIN к выходу QQ1(A<B) при переключении из 0 в 1 – 37 нс.

Рис. 14. Задержка распространения сигнала от входов А, В к выходу QQ2(A=B) при переключении из 0 в 1 – 37 нс.

Представленные задержки не совсем соответствуют табличным (см. табл. 3), но они максимально приближены к ним.

Далее можно сделать выводы по схеме замещения в целом. Она полностью удовлетворяет как требованиям функционального устройства элемента, так и требованиям по динамическим характеристикам разрабатываемого элемента.

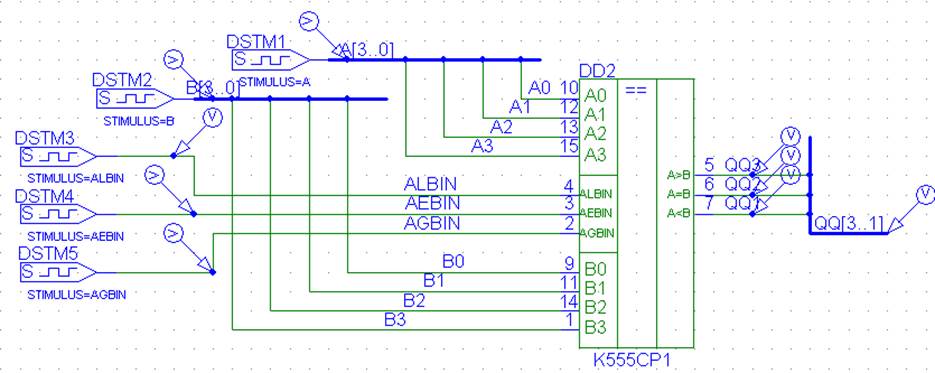

Рис.18. Схема для проверки работоспособности макромодели.

*-------------------------------------- K555CP1 4-разрядныйкомпаратор ------------------------------------

** Начало макромодели

.SUBCKT K555CP1 A3_I A2_I A1_I A0_I B3_I B2_I B1_I B0_I

+ AGBIN_I AEBIN_I ALBIN_I AGBOUT_O AEBOUT_O ALBOUT_O

+ OPTIONAL: DPWR=$G_DPWR DGND=$G_DGND

+ PARAMS: MNTYMXDLY=0 IO_LEVEL=0

*

**Логический блок, в котором зашита функциональность элемента

U85LOG LOGICEXP(11,14) DPWR DGND

+ A3_I A2_I A1_I A0_I B3_I B2_I B1_I B0_I AGBIN_I AEBIN_I ALBIN_I

+ A3 A2 A1 A0 B3 B2 B1 B0 AGBIN AEBIN ALBIN **входы в логический блок

+ AGBOUT AEBOUT ALBOUT **выходы из логического блока

+ D0_GATE

+ IO_STD IO_LEVEL={IO_LEVEL}

+

+ LOGIC:**логическая секция

* BUFFER:

+ A3 = { A3_I }

+ A2 = { A2_I }

+ A1 = { A1_I }

+ A0 = { A0_I }

+ B3 = { B3_I }

+ B2 = { B2_I }

+ B1 = { B1_I }

+ B0 = { B0_I }

+ AGBIN = { AGBIN_I }

+ AEBIN = { AEBIN_I }

+ ALBIN = { ALBIN_I }

+

* INTERMEDIATE TERMS:

+ C3 = { ~(A3 & B3) }

+ C2 = { ~(A2 & B2) }

+ C1 = { ~(A1 & B1) }

+ C0 = { ~(A0 & B0) }

+ A3C3 = { A3 & C3 }

+ A2C2 = { A2 & C2 }

+ A1C1 = { A1 & C1 }

+ A0C0 = { A0 & C0 }

+ B3C3 = { B3 & C3 }

+ B2C2 = { B2 & C2 }

+ B1C1 = { B1 & C1 }

+ B0C0 = { B0 & C0 }

+ D3 = { ~(A3C3 | B3C3) }

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.