\C4_-2\ : IN std_logic;

\D4_-1\ : IN std_logic;

\D4_-2\ : IN std_logic;

\Y4_-1\ : OUT std_logic;

\Y4_-2\ : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic);

END K555LA1;

ARCHITECTURE model OF K555LA1 IS

BEGIN

\Y4_-1\ <= NOT ( \A4_-1\ AND \B4_-1\ AND \C4_-1\ AND \D4_-1\ ) AFTER 1 ns;

\Y4_-2\ <= NOT ( \A4_-2\ AND \B4_-2\ AND \C4_-2\ AND \D4_-2\ ) AFTER 1 ns;

END model;

***********************************Элемент 2ИЛИ*****************************

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

ENTITY K555LL1 IS PORT(

\A7_-1\ : IN std_logic;

\A7_-2\ : IN std_logic;

\A7_-3\ : IN std_logic;

\A7_-4\ : IN std_logic;

\B7_-1\ : IN std_logic;

\B7_-2\ : IN std_logic;

\B7_-3\ : IN std_logic;

\B7_-4\ : IN std_logic;

\Y7_-1\ : OUT std_logic;

\Y7_-2\ : OUT std_logic;

\Y7_-3\ : OUT std_logic;

\Y7_-4\ : OUT std_logic;

VCC : IN std_logic;

GND : IN std_logic);

END K555LL1;

ARCHITECTURE model OF K555LL1 IS

BEGIN

\Y7_-1\ <= ( \A7_-1\ OR \B7_-1\ ) AFTER 1 ns;

\Y7_-2\ <= ( \A7_-2\ OR \B7_-2\ ) AFTER 1 ns;

\Y7_-3\ <= ( \A7_-3\ OR \B7_-3\ ) AFTER 1 ns;

\Y7_-4\ <= ( \A7_-4\ OR \B7_-4\ ) AFTER 1 ns;

END model;

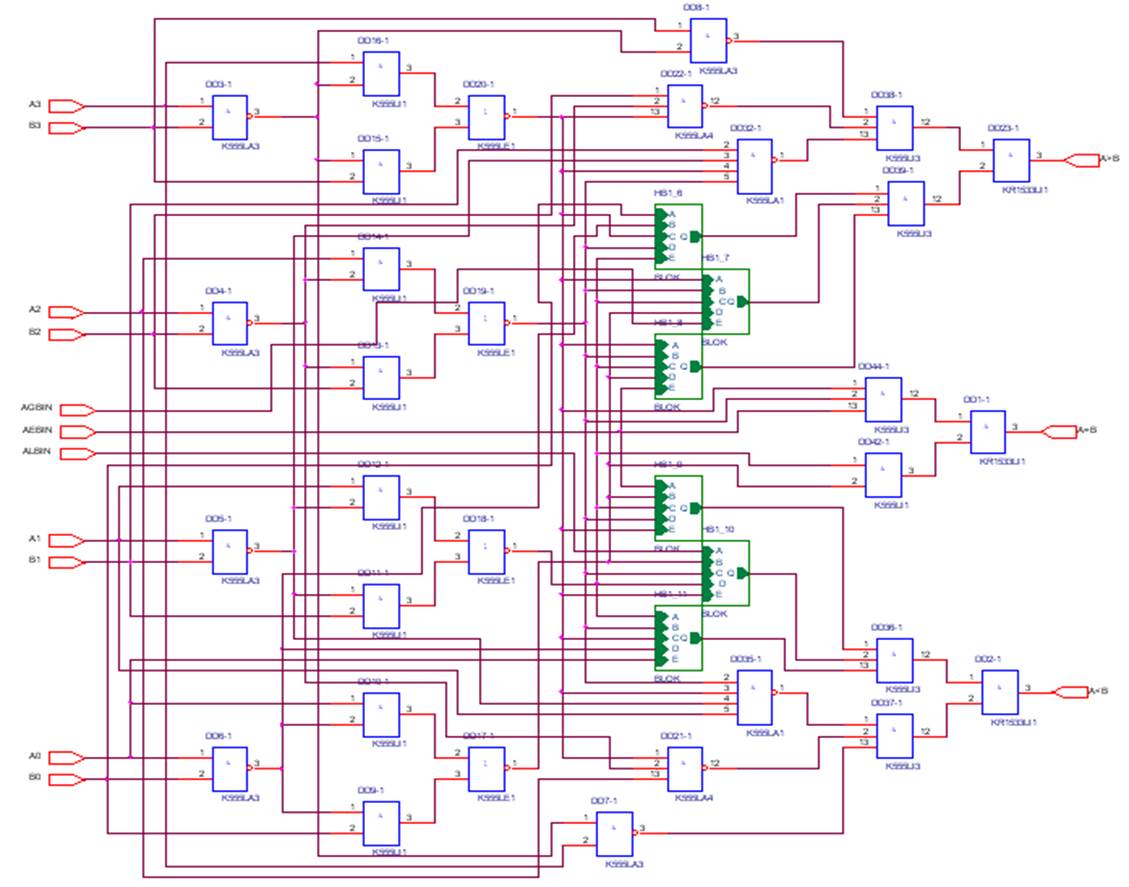

Рис. 34. Схема замещения К555СР1

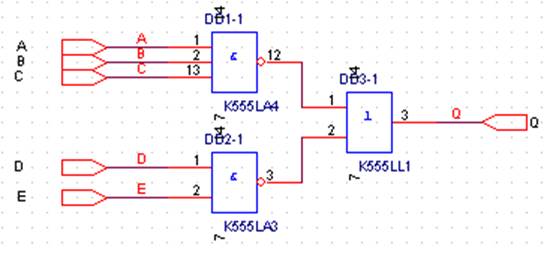

Рис. 35. Содержимое «черного ящика» BLOK.

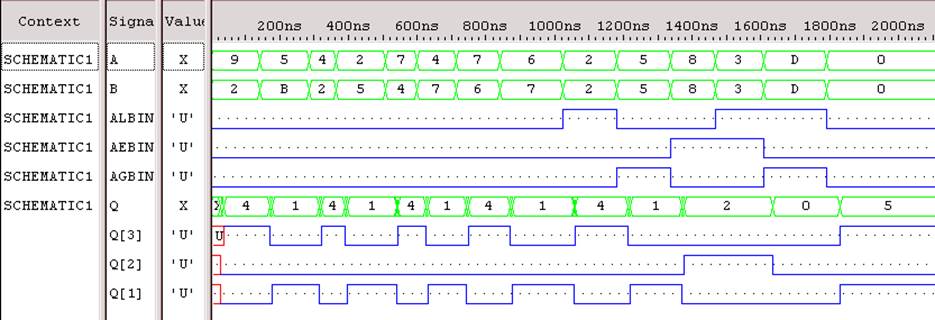

Рис. 36. Результаты работы схемы замещения.

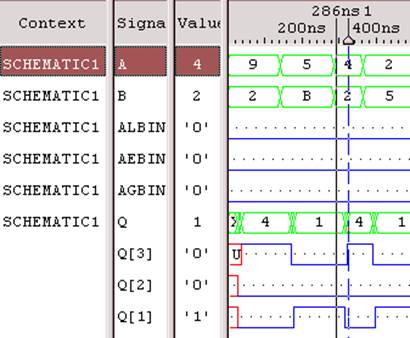

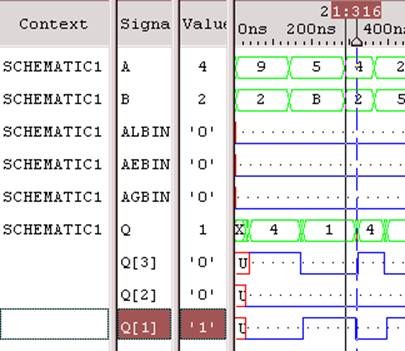

Данная временная диаграмма аналогична временной диаграмме на рис. 5. Далее приводятся временные задержки в различных ситуациях. Все ситуации, аналогичны ситуациям, рассматриваемым ранее при проектировании в пакете DesignLab 8.0.

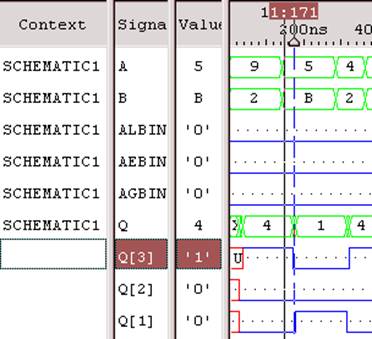

Большим неудобством оказалось то, что данный пакет не выводит окошко с разницей времени между 2-я маркерами. Но эта разница отображается в статусной строке. Первая цифра указывает абсолютное положение маркера D1 на временной линейке, вторая – его положение относительно визирной линейки. Это и есть интересующая нас задержка.

![]()

Рис. 37. Задержка распространения сигнала от входов А,В выходу QQ3(A>B) при переключении из 1 в 0 – 28 нс.

![]()

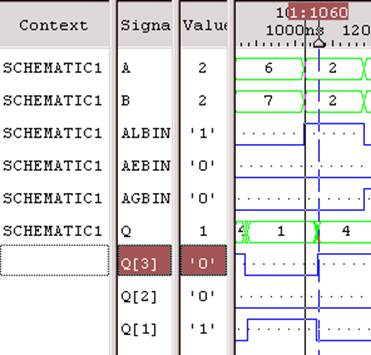

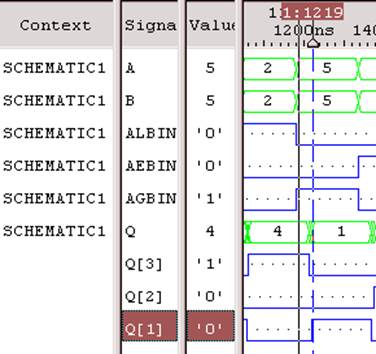

Рис. 38. Задержка распространения сигнала от входов А,В выходу QQ3(A>B) при переключении из 0 в 1 –35 нс.

![]()

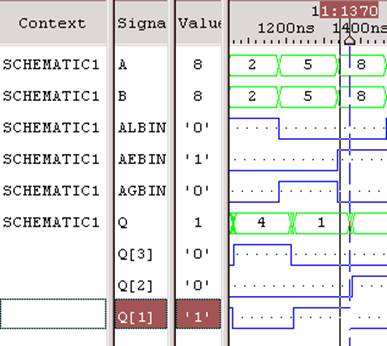

Рис. 39. Задержка распространения сигнала от входа ALBIN выходу QQ3(A>B) при переключении из 0 в 1 –36 нс.

![]()

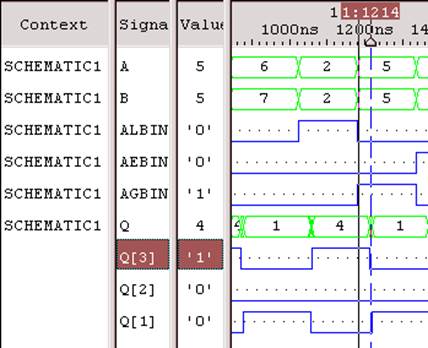

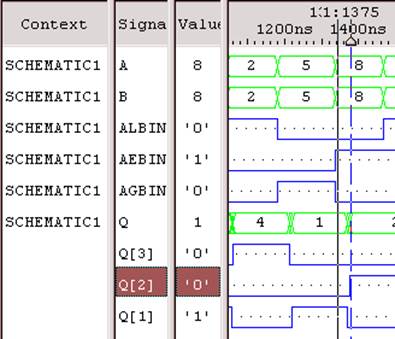

Рис.40. Задержка распространения сигнала от входа ALBIN выходу QQ3(A>B) при переключении из 1 в 0 –32 нс.

![]()

Рис. 41. Задержка распространения сигнала от входов A,B выходу QQ1(A<B) при переключении из 0 в 1 –35 нс.

![]()

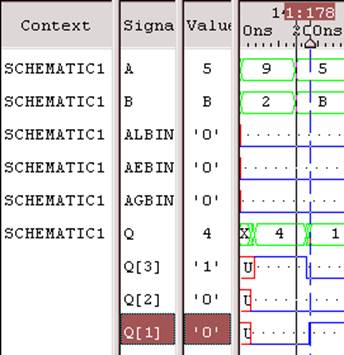

Рис. 42. Задержка распространения сигнала от входов A,B выходу QQ1(A<B) при переключении из 1 в 0 –30 нс.

![]()

Рис. 43. Задержка распространения сигнала от входа AGBIN выходу QQ1(A<B) при переключении из 0 в 1 –37 нс.

![]()

Рис. 44. Задержка распространения сигнала от входа AGBIN выходу QQ1(A<B) при переключении из 1 в 0 –32 нс.

![]()

Рис. 45. Задержка распространения сигнала от входов A,B выходу QQ2(A=B) при переключении из 0 в 1 –37 нс.

![]()

Рис. 46. Задержка распространения сигнала от входов A,B выходу QQ2(A=B) при переключении из 1 в 0 –27 нс.

![]()

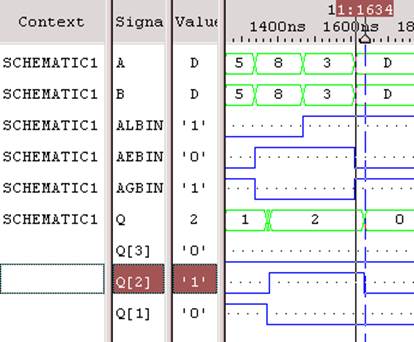

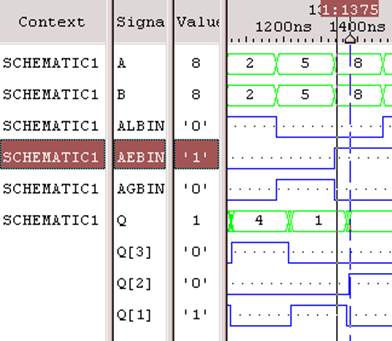

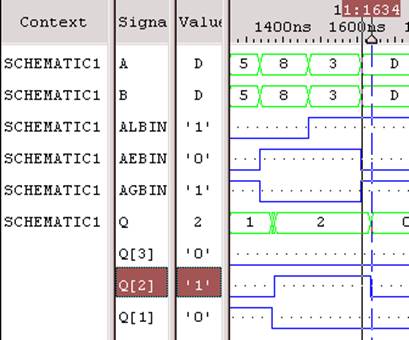

Рис. 47. Задержка распространения сигнала от входа AЕBIN выходу QQ2(A=B) при переключении из 0 в 1 –37 нс.

![]()

Рис. 48. Задержка распространения сигнала от входа AЕBIN выходу QQ2(A=B) при переключении из 1 в 0 –27 нс.

Временные задержки отличаются от табличных, но максимально приближены к ним. Проанализировав полученные временные диаграммы, можно считать, что по функциональным и динамическим параметрам разработанный элемент соответствует своему физическому аналогу.

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE work.orcad_prims.all;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.