ENTITY K555CP1 IS PORT(

A0 : IN std_logic;

A1 : IN std_logic;

A2 : IN std_logic;

A3 : IN std_logic;

B0 : IN std_logic;

B1 : IN std_logic;

B2 : IN std_logic;

B3 : IN std_logic;

AGBIN : IN std_logic;

AEBIN : IN std_logic;

ALBIN : IN std_logic;

\A<B\ : OUT std_logic;

\A=B\ : OUT std_logic;

\A>B\ : OUT std_logic);

END K555CP1;

ARCHITECTURE model OF K555CP1 IS

BEGIN

PROCESS (A0,A1,A2,A3,B0,B1,B2,B3,AGBIN,AEBIN,ALBIN)

BEGIN

IF A3>B3 THEN

\A<B\ <= '0' after 36ns; --Tplh

\A=B\ <= '0' after 30ns; --Tphl

\A>B\ <= '1' after 30ns; --Tphl

ELSIF A3<B3 THEN

\A<B\ <= '1' after 36ns; --Tplh

\A=B\ <= '0';

\A>B\ <= '0' after 30ns; --Tphl

ELSIF A3=B3 AND A2>B2 THEN

\A<B\ <= '0'after 30ns; --Tphl

\A=B\ <= '0';

\A>B\ <= '1'after 36ns; --Tplh

ELSIF A3=B3 AND A2<B2 THEN

\A<B\ <= '1'after 36ns; --Tplh

\A=B\ <= '0';

\A>B\ <= '0'after 30ns; --Tphl

ELSIF A3=B3 AND A2=B2 AND A1>B1 THEN

\A<B\ <= '0' after 30ns; --Tphl

\A=B\ <= '0';

\A>B\ <= '1'after 36ns; --Tplh

ELSIF A3=B3 AND A2=B2 AND A1<B1 THEN

\A<B\ <= '1'after 36ns; --Tplh

\A=B\ <= '0';

\A>B\ <= '0'after 30ns; --Tphl

ELSIF A3=B3 AND A2=B2 AND A1=B1 AND A0>B0 THEN

\A<B\ <= '0'after 30ns; --Tphl

\A=B\ <= '0';

\A>B\ <= '1'after 36ns; --Tplh

ELSIF A3=B3 AND A2=B2 AND A1=B1 AND A0<B0 THEN

\A<B\ <= '1'after 36ns; --Tplh

\A=B\ <= '0';

\A>B\ <= '0'after 30ns; --Tphl

ELSIF A3=B3 AND A2=B2 AND A1=B1 AND A0=B0

AND ALBIN='1' AND AEBIN='0' AND AGBIN='0' THEN

\A<B\ <= '0'after 30ns; --Tphl

\A=B\ <= '0';

\A>B\ <= '1'after 36ns; --Tplh

ELSIF A3=B3 AND A2=B2 AND A1=B1 AND A0=B0

AND ALBIN='0' AND AEBIN='0' AND AGBIN='1' THEN

\A<B\ <= '1'after 36ns; --Tplh

\A=B\ <= '0';

\A>B\ <= '0'after 30ns; --Tphl

ELSIF A3=B3 AND A2=B2 AND A1=B1 AND A0=B0

AND ALBIN='0' AND AEBIN='1' AND AGBIN='0' THEN

\A<B\ <= '0'after 30ns; --Tphl

\A=B\ <= '1'after 36ns; --Tplh

\A>B\ <= '0';

ELSIF A3=B3 AND A2=B2 AND A1=B1 AND A0=B0 AND AEBIN='1' THEN

\A<B\ <= '0';

\A=B\ <= '1';

\A>B\ <= '0';

ELSIF A3=B3 AND A2=B2 AND A1=B1 AND A0=B0

AND ALBIN='1' AND AEBIN='0' AND AGBIN='1' THEN

\A<B\ <= '0';

\A=B\ <= '0'after 30ns; --Tphl

\A>B\ <= '0';

ELSIF A3=B3 AND A2=B2 AND A1=B1 AND A0=B0

AND ALBIN='0' AND AEBIN='0' AND AGBIN='0' THEN

\A<B\ <= '1'after 36ns; --Tplh

\A=B\ <= '0';

\A>B\ <= '1'after 36ns; --Tplh

END IF;

END PROCESS;

END model;

Поведенческая модель оказалась очень простой. Не вызвала у меня особых затруднений. Также легко справилась с реализацией временных задержек.

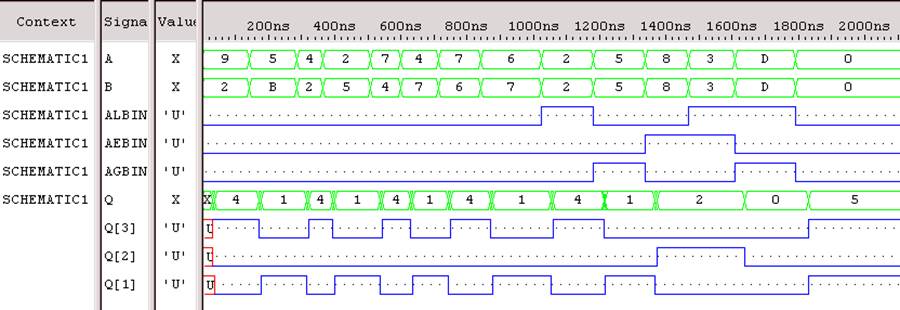

Результаты работы проектируемого узла, подключенного к поведенческой VHDL-модели.

Рис. 49. Временная диаграмма моделируемого узла

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.