+ D2 = { ~(A2C2 | B2C2) }

+ D1 = { ~(A1C1 | B1C1) }

+ D0 = { ~(A0C0 | B0C0) }

+ D32 = { D3 & D2 }

+ D31 = { D32 & D1 }

+ D30 = { D31 & D0 }

+

* OUTPUT ASSIGNMENTS:

+ AGBOUT = { ~B3C3 & ~(B2C2 & D3) & ~(B1C1 & D32) & ~(B0C0 & D31) &

+ ~(ALBIN & D30) & ~(AEBIN & D30) }

+ AEBOUT = { D30 & AEBIN }

+ ALBOUT = { ~(AEBIN & D30) & ~(AGBIN & D30) & ~(A0C0 & D31) &

+ ~(A1C1 & D32) & ~(A2C2 & D3) & ~A3C3 }

*

** Блок задержек. Он отвечает за моделируемые временные задержки

U85DLY PINDLY (3,0,11) DPWR DGND

+ AGBOUT AEBOUT ALBOUT **для каких линий вычисляются задержки

+ A3 A2 A1 A0 B3 B2 B1 B0 AGBINAEBINALBIN**от чего зависят вычисляемые задержки

+ AGBOUT_OAEBOUT_OALBOUT_O**выходные линии блока

+ IO_STD MNTYMXDLY={MNTYMXDLY} IO_LEVEL={IO_LEVEL}

+

+ BOOLEAN:**переменные переключения сигнала

+ DATA_CHANGE = { CHANGED(A3,0) | CHANGED(A2,0) | CHANGED(A1,0) | CHANGED(A0,0)

+ | CHANGED(B3,0) | CHANGED(B2,0) | CHANGED(B1,0) | CHANGED(B0,0) }

+ AEBIN_CHANGE = { CHANGED(AEBIN,0) }

+ ABIN_CHANGE = { AEBIN_CHANGE | CHANGED(ALBIN,0) | CHANGED(AGBIN,0) }

+

+ PINDLY: **та часть, в которой непосредственно генерируются задержки

+ AGBOUT_O ALBOUT_O = { ;AGBOUT & ALBOUT HAS THE SAME DELAY SO CAN BE GROUPPED

+ CASE(

+ DATA_CHANGE & TRN_LH, DELAY(-1,36NS,36NS),

+ DATA_CHANGE & TRN_HL, DELAY(-1,30NS,30NS),

+ ABIN_CHANGE & TRN_LH, DELAY(-1,36NS,36NS),

+ ABIN_CHANGE & TRN_HL, DELAY(-1,30NS,30NS),

+ DELAY(-1,30NS,36NS) ;DEFAULT

+ )

+ }

+ AEBOUT_O = {

+ CASE(

+ DATA_CHANGE & TRN_LH, DELAY(-1,36NS,36NS),

+ DATA_CHANGE & TRN_HL, DELAY(-1,30NS,30NS),

+ AEBIN_CHANGE & TRN_LH, DELAY(-1,36NS,36NS),

+ AEBIN_CHANGE & TRN_HL, DELAY(-1,30NS,30NS),

+ DELAY(-1,30NS,36NS) ;DEFAULT

+ )

+ }

*

.ENDS

*

*$

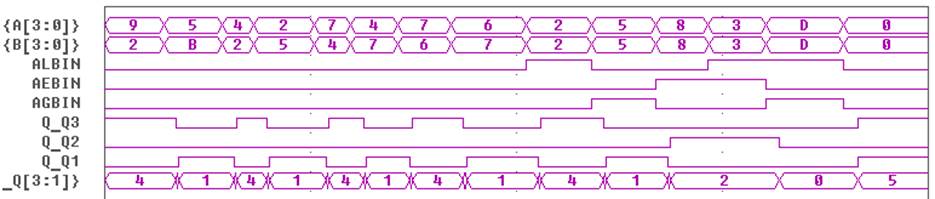

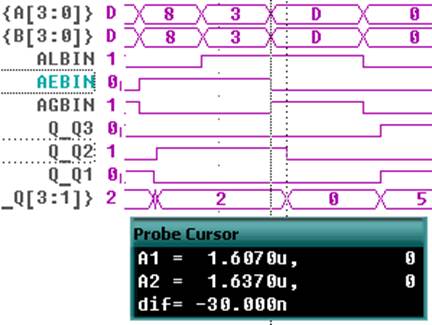

Рис. 19. График из постпроцессора моделирования.

*Примечание: QQ3 – A>B, QQ2 – A=B, QQ1 – A<B.

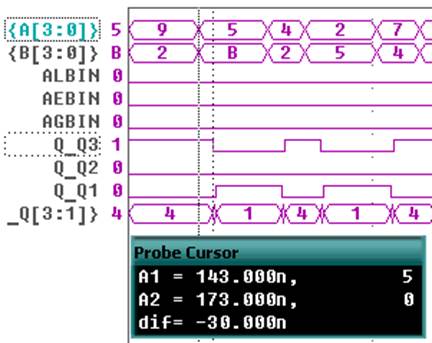

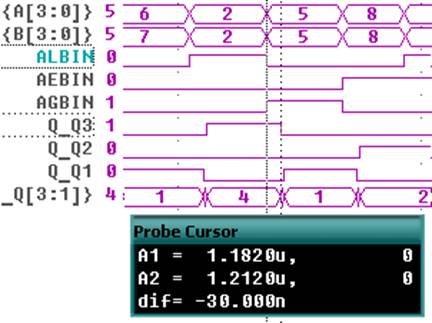

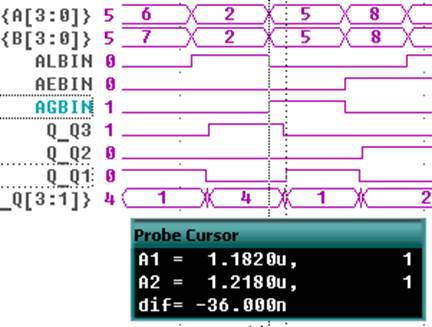

Рис. 20. Задержка распространения сигнала от входов А, В к выходу QQ3(A>B) при переключении из 1 в 0 – 30 нс.

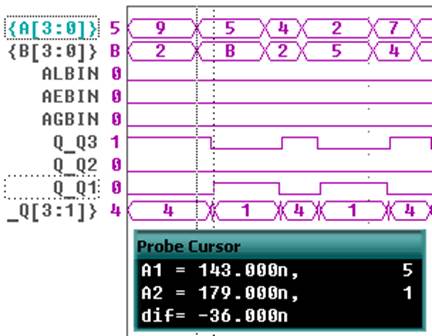

Рис. 21. Задержка распространения сигнала от входов А, В к выходу QQ3(A>B) при переключении из 0 в 1 – 36 нс.

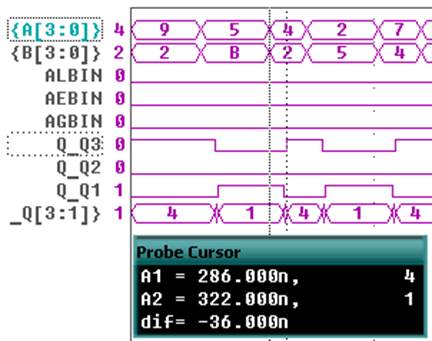

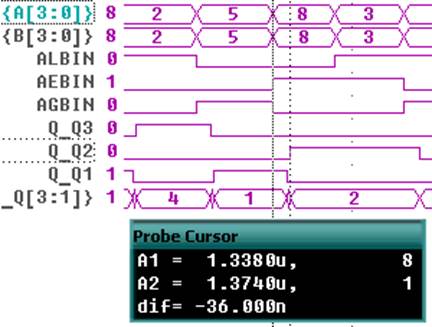

Рис. 22. Задержка распространения сигнала от входа ALBIN к выходу QQ3(A>B) при переключении из 0 в 1 – 36 нс.

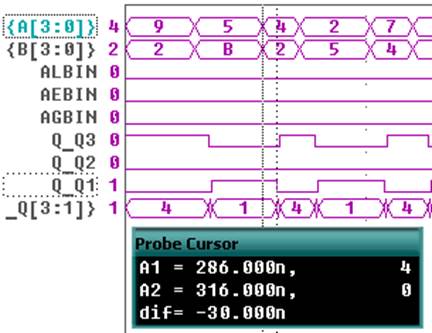

Рис. 23. Задержка распространения сигнала от входа ALBIN к выходу QQ3(A>B) при переключении из 1 в 0 – 30 нс.

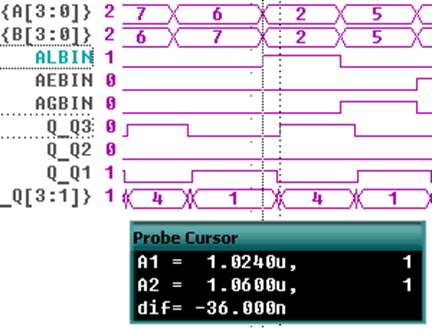

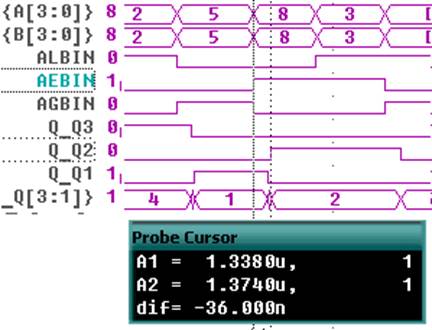

Рис. 24. Задержка распространения сигнала от входов А, В к выходу QQ1(A<B) при переключении из 0 в 1 – 36 нс.

Рис. 25. Задержка распространения сигнала от входов А, В к выходу QQ1(A<B) при переключении из 1 в 0 – 30 нс.

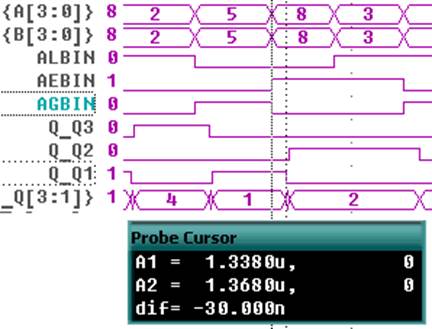

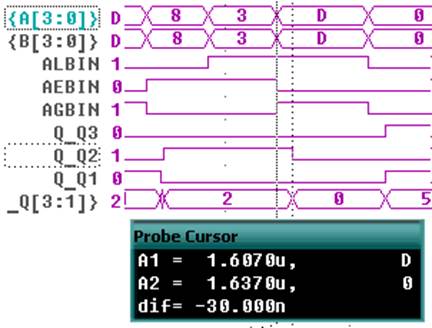

Рис. 26. Задержка распространения сигнала от входа АGВIN к выходу QQ1(A<B) при переключении из 1 в 0 – 30 нс.

Рис. 27. Задержка распространения сигнала от входа АGВIN к выходу QQ1(A<B) при переключении из 0 в 1 – 36 нс.

Рис. 28. Задержка распространения сигнала от входов А, В к выходу QQ2(A=B) при переключении из 0 в 1 – 36 нс.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.