КП МИКРОПРОЦЕССОРЫ

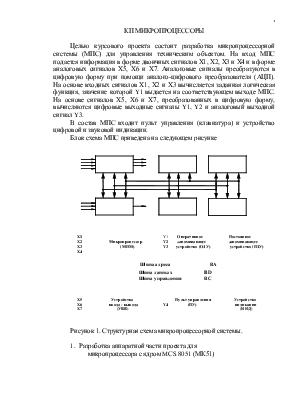

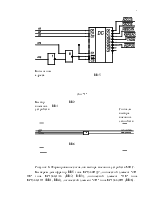

Целью курсового проекта состоит разработка микропроцессорной системы (МПС) для управления техническим объектом. На вход МПС подается информация в форме двоичных сигналов Х1, Х2, Х3 и Х4 и в форме аналоговых сигналов Х5, Х6 и Х7. Аналоговые сигналы преобразуются в цифровую форму при помощи аналого-цифрового преобразователя (АЦП). На основе входных сигналов Х1, Х2 и Х3 вычисляется заданная логическая функция, значение которой Y1 выдается на соответствующем выходе МПС. На основе сигналов Х5, Х6 и Х7, преобразованных в цифровую форму, вычисляются цифровые выходные сигналы Y1, Y2 и аналоговый выходной сигнал Y3.

В состав МПС входит пульт управления (клавиатура) и устройство цифровой и звуковой индикации.

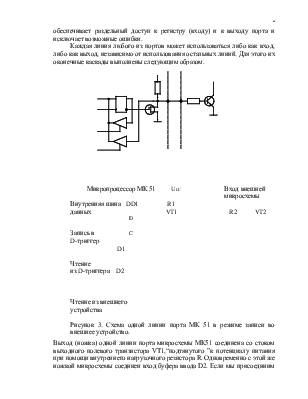

Блок схема МПС приведена на следующем рисунке

X1 Y1 Оперативное Постоянное

X2 Микропроцессор Y2 запоминающее запоминающее

X3 (МПМ)Y3 устройство (ОЗУ) устройство (ПЗУ)

X4

Шина адреса ВА

Шина данных BD

X5 Устройство Пульт управления Устройство

X6 ввода - выводаY4 (ПУ) индикации

X7 (УВВ) (ИНД)

Рисунок 1. Структурная схема микропроцессорной системы.

1. Разработка аппаратной части проекта для микропроцессора с ядром MСS 8051 (МК51)

1.1 Структурная схема микропроцессора МК51.

Микропроцессоры с архитектурой и системой команд (ядром), разработанных фирмой Intel для микропроцессора MCS 8051, пользуются большой популярностью и выпускаются многими производителями. Широко известны отечественный микропроцессор КМ1816БЕ51, микропроцессор AT89C51 фирмы ATMEL или P87LPC769 фирмы Philips Semiconductors. Отличительной особенностью микропроцессоров этого типа является высокое быстродействие (тактовая частота до 40 МГц) и простота программирования. Микропроцессор КМ1816БЕ51 содержит следующие основные блоки:

- резидентную память ( стираемое ПЗУ программ емкостью 4К и ОЗУ данных емкостью 128 байт),

- арифметико-логическое устройство (АЛУ), включающее схемы аппаратной реализации команд умножения и деления,

- блок регистров специальных функций,

- устройство управления,

- программируемые порты ввода-вывода (32 вывода),

- блок двухуровнего векторного прерывания (5 линий),

- асинхронный порт двухстороннего (дуплексного) последовательного ввода - вывода.

Эти блоки связаны между собой 8-ми битной общей шиной. Микропроцессор МК51 может работать в диапазоне тактовых частот от 1.2 до 12 МГц, при этом минимальное время цикла выполнения команд равно 1 мкс.

8-ми битное АЛУ может выполнять арифметические и логические операции. В состав АЛУ входят два программно недоступных регистров Т1 и Т2, предназначенные для временного хранения операндов. АЛУ может оперировать следующими типами данных: логическими (1 бит), цифровыми (4 бита), байтными (8 бит) и адресными (16 бит).

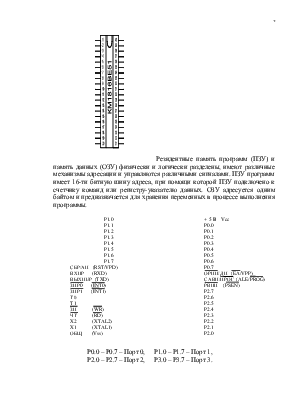

Резидентные

память программ (ПЗУ) и память данных (ОЗУ) физически и логически разделены,

имеют различные механизмы адресации и управляются различными сигналами. ПЗУ

программ имеет 16-ти битную шину адреса, при помощи которой ПЗУ подключено к

счетчику команд или регистру-указателю данных. ОЗУ адресуется одним байтом и

предназначается для хранения переменных в процессе выполнения программы.

Резидентные

память программ (ПЗУ) и память данных (ОЗУ) физически и логически разделены,

имеют различные механизмы адресации и управляются различными сигналами. ПЗУ

программ имеет 16-ти битную шину адреса, при помощи которой ПЗУ подключено к

счетчику команд или регистру-указателю данных. ОЗУ адресуется одним байтом и

предназначается для хранения переменных в процессе выполнения программы.

P1.0 + 5 B Vcc

P1.1 P0.0

P1.2 P0.1

P1.3 P0.2

P1.4 P0.3

P1.5 P0.4

P1.6 P0.5

P1.7 P0.6

СБР/АП (RST/VPD) P0.7

![]()

![]() ВХПР (RXD) ОРПП/ДП (EA/VPP)

ВХПР (RXD) ОРПП/ДП (EA/VPP)

![]()

![]() ВЫХПЕР (TXD) САВП/ПРОГ

(ALE/PROG)

ВЫХПЕР (TXD) САВП/ПРОГ

(ALE/PROG)

![]()

![]()

![]()

![]() ЗПР0 (INT0)

РВПП (PSEN)

ЗПР0 (INT0)

РВПП (PSEN)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.