Приемник А (элемент В8) и приемник В (элемент А8) осуществляют прием сигналов от БСС частотой 8,192 МГц и 8 кГц (обозначенных как 8М и 8К) из дифференциальных линий связи А и В соответственно.

Узел выбора каналов (элементы D8, D5.2, D5.4, D5.8, D5.10, D7, С8, D6, D29) по сигналу МОDЕ производит выбор одного из каналов синхронизации, вырабатывая сигналы разрешения DЕNА и DЕNВ соответственно, сигнал 8М (частотой 8,192 МГц), использующийся для синхронизации счетчиков, и сигнал установки счетчиков РЕ/.

Если МОDЕ = 0, то выбирается канал А, если МОDЕ = 1, то выбирается канал В. После подачи питания – сигнал МОDЕ = 0. При изменении значения сигнала МОDЕ на противоположное сигналы DЕNА и DЕNВ привязываются к тактовой частоте выбранного канала и переключаются с задержкой на такт.

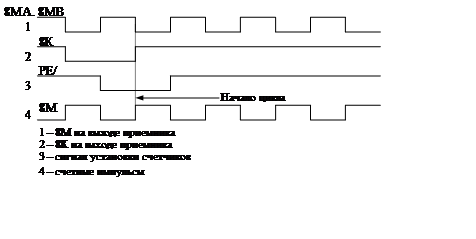

Формирование счетных импульсов 8М и сигнала установки счетчиков РЕ/ показано на рисунке 5.12. Счетчик 1 (элементы D2, С1, D4), счетчик 2 (элементы D1, С2) и регистр 1 (элемент С5) используются для формирования необходимой сетки синхрочастот, которые через шинный формирователь 1 (элементы В1, D3, С4) и передатчик (элементы АЗ, А4, ВЗ, СЗ) поступают на разъем X1. С помощью перемычек можно получать сетки частот, отличающиеся по фазе, меняя код установки счетчиков:

для счетчика 1 – 0,1,2,3;

для счетчика 2 – FС, FО, FЕ, FF.

|

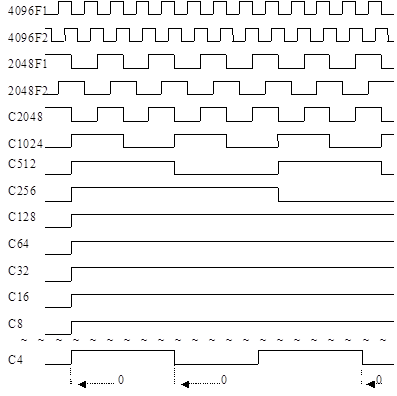

Временные диаграммы выходных сигналов блока модификации БМС приведены на рисунке 5.13.

Цифровой компаратор (элемент А1) производит выбор данного блока, вырабатывая сигнал SЕ1 при совпадении кода А7/, А8/, А9/, А10/ и S0, S1, S2, S3.

Дешифратор (элементы В6.12, В5) производит выбор портов блока при единичном значении сигнала SEL и значениях адресных сигналов А5/ и А6/, определенных в таблице 5.2.

Узел формирования управляющих сигналов (элементы В2, В4.3, В4.11, В4.8, В6.8, В6.10, В4.6) осуществляет прием сигналов I/ОR/, I/ОW/ с магистрали расширения и вырабатывает сигналы стробирования дешифратора, сигнал разрешения буфера данных: DЕ/ = (SЕL&(I/ОR/&I/OW/)/)/; сигнал направления передачи данных DI/R, который является инверсией сигнала I/ОR/.

Буфер данных (элемент А2) служит для подключения 8-разрядной шины данных блока к шине данных расширения системы ВD0/–ВD7/.

Шинный формирователь 2 и шинный формирователь 3 предназначены для передачи в процессор состояния 16 контрольных сигналов SТ0–SТ15.

Регистр 2 и регистр 3 формируют 16 управляющих сигналов СТR0–СТR15, которые через шинный формирователь 4 и шинный формирователь 5 подаются на разъем Х2.

Рисунок 5.13 – Временные диаграммы сигналов блока местной синхронизации модификации БМС

Таблица 5.2

|

Сигнал |

А6/ |

А5/ |

Операция |

Назначение |

|

WR1/ RD1/ |

0 0 |

0 0 |

Запись в регистр 2 Чтение шинного формирователя 1 |

Выходные сигналы CTR 0–7 Опрос контрольных сигналов ST0–ST7 |

|

WR2/ RD2/ |

0 0 |

1 1 |

Запись в регистр 3 Чтение шинного формирователя 2 |

Выходные сигналы CTR 8–15 Опрос контрольных сигналов ST8–ST15 |

|

WR3/ |

1 |

0 |

Запись (сброс триггера 1) |

Подключение к шине сигналов CTR0–CTR15 |

|

RD3/ |

1 |

0 |

Чтение (установка триггера 2) |

Выбор канала В |

|

WR4/ |

1 |

1 |

Запись (сброс триггера 2) |

Выбор канала А |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.